时序逻辑电路分析与设计d大神, 这个怎么画呀?

xxpiudsa2022-10-04 11:39:541条回答

xxpiudsa2022-10-04 11:39:541条回答

已提交,审核后显示!提交回复

共1条回复

雪吻梅 共回答了20个问题

雪吻梅 共回答了20个问题 |采纳率85%- D触发器是时钟下降沿边沿触发,所以只要看CP的下降沿对应的D输入和Q的状态就行了,CP下降沿时,如果Q与D不同,则Q=D,其它情况下,Q保持不变

- 1年前

相关推荐

- 时序逻辑电路的基本单元是什么?

剑梦十三少1年前1

剑梦十三少1年前1 -

公猫和母野筱猫 共回答了24个问题

公猫和母野筱猫 共回答了24个问题 |采纳率91.7%锁存器 触发器1年前查看全部

- 下列逻辑电路中为时序逻辑电路的是 .A、译码器 B、加法器 C、寄存器 D、数据选择器

brucej1年前1

brucej1年前1 -

不喜欢喝水 共回答了14个问题

不喜欢喝水 共回答了14个问题 |采纳率78.6%C1年前查看全部

- 1、时序逻辑电路的输出信号:A、与当时的输入信号有关,与电路的原状态无关.B、与当时的输入信号有关,

1、时序逻辑电路的输出信号:A、与当时的输入信号有关,与电路的原状态无关.B、与当时的输入信号有关,

1、时序逻辑电路的输出信号:

A、与当时的输入信号有关,与电路的原状态无关.B、与当时的输入信号有关,与电路的原状态有关.

C、与当时的输入信号无关,与电路的原状态有关.D、

2、时序逻辑电路中必须含有:

A、存储电路 B、编码器

C、加法器 D、

3、同步时序逻辑电路所有触发器的时钟输入端都接同一个时钟脉冲.

A、各触发器不同时具备触发翻转的条件 B、各触发器同时具备触发翻转的条件

C、各触发器的触发翻转有先有后 D、

4、异步时序逻辑电路各触发器的时钟输入所接不是同一的时钟脉冲.

A、结构简单,B、结构复杂,

C、结构简单,D、

5、异步时序逻辑电路,各触发器:

A、触发翻转有先有后 B、同时触发翻转

C、无法确定 D、

第二题、多项选择题(每题2分,

1、时序逻辑电路从结构上讲,包含有:

A、存储元件

B、触发器或含有反馈延迟电路

C、译码器

2、时序逻辑电路的输出信号:

A、与当时的输入信号无关

B、与当时的输入信号有关

C、与电路的原状态有关

D、与电路的原状态无关

3、同步时序逻辑电路:

A、所有触发器的时钟输入端都接同一个时钟脉冲

B、各触发器同时具备触发翻转的条件

4、时序逻辑电路的逻辑功能可用( )来描述.

A、状态方程

B、状态表

C、状态图

D、时序图

5、时序逻辑电路的分析是指已知逻辑图:

A、列写逻辑方程式

B、计算状态表

C、画电路的状态图

D、画电路的时序图

E、判定电路的功能

第三题、判断题(每题1分,

1、时序逻辑电路中必须含有存储电路.

正确 错误

2、时序逻辑电路中的存储电路只能用延迟元件组成,不能用触发器构成.

正确 错误

3、同步时序逻辑电路各触发器同时具备触发翻转的条件.

正确 错误

4、异步时序逻辑电路结构简单,

正确 错误

5、时序逻辑电路的输出信号只与当时的输入信号有关,与电路的原状态无关.

正确 错误 qianyangyang1年前2

qianyangyang1年前2 -

高阳16 共回答了15个问题

高阳16 共回答了15个问题 |采纳率80%1b 2a 3b 4d具体电路决定,无法比较 5d由其独自时钟信号决定

1ab 2bc 3ab 4bcd 5abcde

对 错 对 错 错1年前查看全部

- 关于数电的一个疑问,关于时序逻辑电路的输出信号的表示问题

关于数电的一个疑问,关于时序逻辑电路的输出信号的表示问题

时序电路的表示函数(特征方程)一般通过卡诺图(状态转换表)得到,进而可以用相关器件连出电路图,但卡诺图和状态转换表均是描述现态和次态关系的工具,为什么所有的数电书上都把电路的输出信号也放在卡诺图和状态转换表里描述?要知道输出信号的电路是门电路组成的啊!门电路又没有记忆功能,如何能用现态表示输出的次态?不知道表述是否完善,我会追问 asdlaw1年前3

asdlaw1年前3 -

樱焰枫冰 共回答了17个问题

樱焰枫冰 共回答了17个问题 |采纳率94.1%你说的对,数电最基本的时序电路,可以用卡诺图求得.虽然看不太懂你所问的问题.不过跟你说,数电这门课程,学到后期卡诺图和状态转换表可以全部抛弃,因为已经深植与你的脑海中.现在书上给你一个输出信号的描述,就是为了方便你更容易理解卡诺图、状态图云云.注意你面对的是时序逻辑电路,而不是组合逻辑电路.当你知道当前环节(当前时序)一个点的位置(状态)后,那么顺着这个点会很好推出下一个点(状态)的状态.也就是你所谓的由现态表示次态.1年前查看全部

- 时序逻辑电路的主要组成部分.组合逻辑电路的主要组成部分.

时序逻辑电路的主要组成部分.组合逻辑电路的主要组成部分.

简要说明 虎躯大震1年前1

虎躯大震1年前1 -

yeemee 共回答了16个问题

yeemee 共回答了16个问题 |采纳率93.8%触发器是时序逻辑电路的主要组成部分.触发器是由逻辑门 加反馈信号构成的,具有存储数据、记忆信息等多种功能.

逻辑门是组合逻辑的主要组成部分.1年前查看全部

- 1、时序逻辑电路从结构上讲,包含有:

1、时序逻辑电路从结构上讲,包含有:

A、存储元件

B、触发器或含有反馈延迟电路

C、译码器

2、2、时序逻辑电路的输出信号:

A、与当时的输入信号无关

B、与当时的输入信号有关

C、与电路的原状态有关

D、与电路的原状态无关

3、3、同步时序逻辑电路:

A、所有触发器的时钟输入端都接同一个时钟脉冲

B、各触发器同时具备触发翻转的条件

C、速度快;结构简单

D、速度快;结构复杂

4、4、时序逻辑电路的逻辑功能可用( )来描述.

A、状态方程

B、状态表

C、状态图

D、时序图

5、5、时序逻辑电路的分析是指已知逻辑图:

A、列写逻辑方程式

B、计算状态表

C、画电路的状态图

D、画电路的时序图

E、判定电路的功能

多选题 wsk12341年前1

wsk12341年前1 -

hxpvaj 共回答了16个问题

hxpvaj 共回答了16个问题 |采纳率81.3%1AB;2C;3AC;4ABCD;5ABCDE1年前查看全部

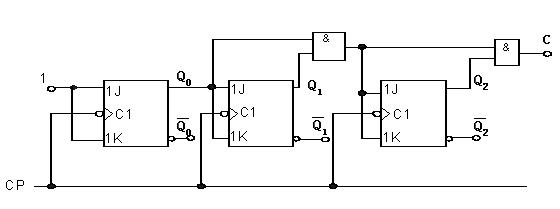

- 分析下列时序逻辑电路,假设触发器的初始状态为0.要求:

分析下列时序逻辑电路,假设触发器的初始状态为0.要求:

求出状态方程、列写状态表、画出状态图;

此电路能否自启动?

supretard1年前1

supretard1年前1 -

wangxing3020 共回答了18个问题

wangxing3020 共回答了18个问题 |采纳率88.9%没分啊,不干

看了一眼,没列方程,仅仅是粗略地读了一下图.是个同步加1八进计数器,按自然二进制码循环的,可以自启动.

你还是弄点分给我吧.1年前查看全部

- 时序逻辑电路和组合逻辑电路的区别有哪些

hanxuezhi20081年前1

hanxuezhi20081年前1 -

8883693 共回答了22个问题

8883693 共回答了22个问题 |采纳率81.8%组合逻辑电路是输出只与当前的输入有关,而时序逻辑电路的输出不仅与当前的输入有关还与电路以前的状态有关.也就是说时序逻辑电路有记忆功能的元件,如各种触发器等.1年前查看全部

- 数字电子技术中,已知时序逻辑电路的工作波形,如何设计相关电路?

hamapiu1年前1

hamapiu1年前1 -

afgsddzs 共回答了20个问题

afgsddzs 共回答了20个问题 |采纳率100%我一般是这么做:

1.根据波形列出输入输出相关变量的真值表

2.根据真值表,写出输入输出的逻辑表达式

3.化简逻辑表达式,简单的可以直接根据规则化简,复杂的可借助卡诺图化简

4.开始设计电路,根据已有器件的真值表对照需要达成的逻辑功能进行设计.这里我说的比较简略,主要是没法详细说,因不同的电路,不同的逻辑功能会有很大的不同,不能一概而论哈~

5.检验已设计的电路,有条件的可以借助电脑仿真,比如使用QuatusII 等软件1年前查看全部

- 同步时序逻辑电路和异步时序逻辑电路有何不同?

OIOM1年前1

OIOM1年前1 -

感性米 共回答了16个问题

感性米 共回答了16个问题 |采纳率87.5%同步时序电路只有一个时钟源,也就是说这个电路中的每一个触发器都是同时被触发

异步时序电路有多个时钟源,也就是说,每个触发器不是同时被触发的,有时间先后.

其他的不同就是,异步时序电路普遍比同步时序电路复杂.1年前查看全部

- 半加器和全加器是否属于时序逻辑电路?

绿豆之绿1年前1

绿豆之绿1年前1 -

吹牛岂用草稿 共回答了24个问题

吹牛岂用草稿 共回答了24个问题 |采纳率87.5%不属于.1年前查看全部

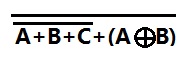

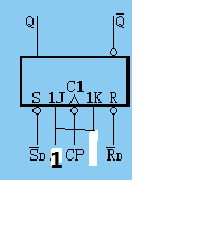

- 数字电子技术的逻辑函数化简问题,还有几个关于数字电路,TTL.时序逻辑电路这方面的问题,

数字电子技术的逻辑函数化简问题,还有几个关于数字电路,TTL.时序逻辑电路这方面的问题,

① 数字逻辑中的“异或”怎么化简 比如这个式子:

怎么化简成最简与或表达式

②怎么由电路图看出电路构成的是几进制的计数器?

比如有一道题说:所示电路是由74161构成的N进制计数器,其N=___

这个N要怎么看出来

③TTL与非门在VCC和输出端Y之间接电阻是什么意思

一道题让求这个之间所接电阻的值的范围 怎么求

④时序逻辑电路的状态图怎么看?

比如 :00→(箭头上面是“/1”)01

这个“/1”代表什么意思?

还有一道题:

如图所示电路中:若A=0,B=1

图:

为什么Q=1与CP无关?

就是S对应A,R对应B啦。这题本来是有两个选项的,Q=0与CP无关 或 Q=1与CP无关。我想问问为什么选Q=1与CP无关呢?Q=0与CP有关么?

另外再问问,怎么用十进制计数器相连实现各种多进制的计数器?能用易懂一些的语言描述一下么? 火锅1231年前3

火锅1231年前3 -

hfjccljm 共回答了14个问题

hfjccljm 共回答了14个问题 |采纳率100%A异或B可以表示成:AB非+A非B ,用这样的形式去掉原式中的“异或”“同或”.再根据摩根定律和逻辑代数的方法一般就可以化简成 最简与或式.如果遇到原式十分复杂的情况,可以用“卡诺图”来化简,其步骤一般是:(1)将...1年前查看全部

- 时序逻辑电路与组合逻辑电路最大的区别是什么?

119xianger1年前1

119xianger1年前1 -

yifei3018 共回答了28个问题

yifei3018 共回答了28个问题 |采纳率92.9%组合逻辑电路的输出只取决于当前的输入值.

而时序逻辑电路的输出,不仅取决于当前的输入值,还与当前电路所处的状态有关.也就是说时序逻辑电路一定有记忆功能的元件,如各种触发器,寄存器等.1年前查看全部

- 数字电路中逻辑表达式值大于一怎么办?例如在时序逻辑电路中Q3=Q1+Q2,Q1和Q2 都为1时

老ss1年前1

老ss1年前1 -

微雨清寒 共回答了14个问题

微雨清寒 共回答了14个问题 |采纳率92.9%在逻辑运算里面,1+1=1,所以,当Q1和Q2 都为1时,Q3=Q1+Q2=1+1=1.

逻辑运算的结果只有0和1,没有其它结果.1年前查看全部

- 数电方面关于时序逻辑电路的问题分析电路的功能的时候,是看的状态方程对应的结果吧,也就是Q的次态,那输出起什么作用呐,还是

数电方面关于时序逻辑电路的问题

分析电路的功能的时候,是看的状态方程对应的结果吧,也就是Q的次态,那输出起什么作用呐,还是说我这样理解就是错的 micky_0060swj1年前1

micky_0060swj1年前1 -

w_w太阳 共回答了21个问题

w_w太阳 共回答了21个问题 |采纳率81%分析电路的功能:

电路--->输出方程,状态方程,驱动方程,特性方程,时钟方程---->状态图--->分析1年前查看全部

- 分析如下时序逻辑电路,说明电路实现的逻辑功能.计算机电路基础的课程

结巴结巴结巴1年前1

结巴结巴结巴1年前1 -

曾经的美好 共回答了12个问题

曾经的美好 共回答了12个问题 |采纳率100%这是一个2位同步可逆二进制计算器,x=0时是加法计数

x=1时是减法计数

先写出电路的时钟方程、驱动方程和状态方程

再列状态转换真值表,从表中可看出其规律(几个状态即为几进制)

当然有些电路还要检查自启动1年前查看全部

- 组合逻辑电路与时序逻辑电路的区别?

wp84251年前1

wp84251年前1 -

gai1011 共回答了18个问题

gai1011 共回答了18个问题 |采纳率83.3%时序电路具有记忆功能.时序电路的特点是:输出不仅取决于当时的输入值,而且还与电路过去的状态有关.

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关1年前查看全部

- 关于时序逻辑电路__.下列电路中,不属于时序逻辑电路的是_______.A.计数器B.触发器 C.寄存器 D.译码器

sket261年前1

sket261年前1 -

紫夜_lovegoogol 共回答了13个问题

紫夜_lovegoogol 共回答了13个问题 |采纳率76.9%D1年前查看全部

- 时序逻辑电路中的时钟是什么意思

一烟难烬1年前1

一烟难烬1年前1 -

简单爱jay 共回答了17个问题

简单爱jay 共回答了17个问题 |采纳率94.1%这样做个比方吧,时钟就相当于人的心跳速率.心跳慢了不行,会供血不足;但是心跳快了也不行,会高血压,嘿嘿.你这里所说的时序逻辑电路的时钟是控制时序逻辑电路状态转换的“发动机”,没有它时序逻辑电路就不能正常工作,...1年前查看全部

- 什么是同步与异步时序逻辑电路概念及其优缺点

金属鼠标1年前1

金属鼠标1年前1 -

九灵龙 共回答了18个问题

九灵龙 共回答了18个问题 |采纳率94.4%1.同步时序电路:同步时序电路是指各触发器的时钟端全部连接在一起,并接系统时钟端;只有当时钟脉冲到来时,电路的状态才能改变;改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x有无变化;状态表中的每个状态都是稳定的.

2.异步时序电路:异步时序电路是指电路中除以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路中没有统一的时钟;电路状态的改变由外部输入的变化直接引起.可将异步时序逻辑电路分为脉冲异步时序电路和电平异步时序电路.1年前查看全部

- 组合逻辑电路和时序逻辑电路在逻辑功能与电路结构上有何区别?

凌峰10171年前1

凌峰10171年前1 -

田仲俊贤 共回答了14个问题

田仲俊贤 共回答了14个问题 |采纳率100%组合逻辑电路的输出只与输入有关,时序逻辑电路的输出不仅与输入有关还与初始状态有关.

它们逻辑功能与电路结构都是具体问题具体分析,但明显与初始状态有关的即是由时序逻辑电路实现.很多情况下二者都会结合应用.1年前查看全部

- 时序逻辑电路是什么?

雙重性格1年前1

雙重性格1年前1 -

我是网吧 共回答了21个问题

我是网吧 共回答了21个问题 |采纳率90.5%需要脉冲电路的一种数字电路,分为同步和异步1年前查看全部

- 时序电路时序电路中必须包含( )以便保存电路状态,因此,时序电路的输出是( )和( )的函数.常见的时序逻辑电路有( )

时序电路

时序电路中必须包含( )以便保存电路状态,因此,时序电路的输出是( )和( )的函数.常见的时序逻辑电路有( )、( )和( )等.时序电路常用的表示方法有哪四种? 自学不息1年前1

自学不息1年前1 -

hellykity 共回答了9个问题

hellykity 共回答了9个问题 |采纳率88.9%考试呀 童靴1年前查看全部

- 时序逻辑电路可以分为同步时序逻辑电路和____两类?

无法再爱谁1年前1

无法再爱谁1年前1 -

j560115 共回答了15个问题

j560115 共回答了15个问题 |采纳率86.7%按CP作用分同步时序电路和异步时序电路;

按电路输出信号的特性分摩尔型Moore和米里型Mealy;

按逻辑功能分计数器、寄存器、移位寄存器、读/写存储器、顺序脉冲发生器等.1年前查看全部

大家在问

- 1一种洗衣机原价900元,降价18分之1后,现价多少元?

- 2甲乙两数的比是7︰3,甲数比乙数多36.乙数是( ).

- 3猜一猜,他们看到的可能是什么物体? 从右边看到的是○. 从正面和上面看到的都是长方形

- 4太阳与银河系的中心相距约为多少光年

- 5Our English teacher always _____ a smile on her face. [

- 6【初一英语】汉语提示完成句子1.请不要躺在床上看书._____ ______ read ______ bed.2.在会议

- 7请坐下 please have a seat=please sit down =please()()()

- 8球体的体积公式

- 9初二物理关于光的反射规律的 用物理学的角度回答 急用

- 10mistake a for b是将a误认为b还是反之

- 11---I have finished my homework ,let’s watch the program I AM

- 129-(根号13的小数部分)与9+(根号13的小数部分)=a和b 求4a+4b

- 13降压电路12V降到5V要用多少欧的电阻

- 14请教英语代词 在线to stay wake,he finishe a cup of coffee and odered

- 15Must we finish the work before five?