74LS161的cet和cep有什么不同?

枯藤石头2022-10-04 11:39:541条回答

枯藤石头2022-10-04 11:39:541条回答

已提交,审核后显示!提交回复

共1条回复

小猪1117 共回答了13个问题

小猪1117 共回答了13个问题 |采纳率92.3%- CET是计数控制端,CEP是使能端(低电平有效)

- 1年前

相关推荐

- 5、试用74LS161构成十进制计数器,要求画出线路图,

大家来看1年前0

大家来看1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 请教74LS161计数器级联进制计算的问题?

请教74LS161计数器级联进制计算的问题?

预置数为0111 1001 (对应二进制数为121)

方法一: 就是用计数器最大值 -预置数 就得到256-121=135进制

方法二:对于低位计数器预置数是1001 它循环一次的模就是7(也就是循环一次到1111 总共有7个状态),对于高位计数器,它的模就是9,。那么低位可以看成是7进制的计数器,高位的可以看成9进制的计数器 级联以后的进制就是7*9=63进制。 此题答案是A.

我的问题是为什么第一种方法在此是错的,因为很多级联的计数器进制都是可以用第一种方法计算的

精灵笨鼠1年前1

精灵笨鼠1年前1 -

红叶题 共回答了21个问题

红叶题 共回答了21个问题 |采纳率90.5%这两个芯片,置数的操作,不是同时进行的。

所以《方法2》的分析,是正确的。

左边的芯片,实际上是7进制。

右边的芯片,实际上是9进制。

级联后,就是 63 进制。

《方法1》的分析,适用于同时置数。1年前查看全部

- 用CD4046和74LS161 组成的锁相环频率合成器 要求输出频率300~400k

momosu1年前1

momosu1年前1 -

79啊3 共回答了17个问题

79啊3 共回答了17个问题 |采纳率100%频率合成:CD4046和8253组成的锁相环中,fo=100N 其中8253的定时器做4046的当输出幅度为5V时,DAC输入数值应为400.因为题目要求的最高 幅度为5V,1年前查看全部

- 数字电子技术题(超基础的)1:请用74LS161构成一个从1到12的十二进制的计数器.2:用8选1数据选择器74LS15

数字电子技术题(超基础的)

1:请用74LS161构成一个从1到12的十二进制的计数器.

2:用8选1数据选择器74LS151实现下列逻辑函数

F2(A,B,C)= ∑m(1,2,3,5,7)

3:用卡诺图化简法将下列函数化简为最简或表达式.

Y(A ,B,C)=∑m()0,1,2,4,5,6)

就这3题 不过我没学,都是书本上的题,只是我没学,但又要考 ,郁闷!请会的

第一题我会了 可以不用做,现在要第2,3题 cycqjh1年前0

cycqjh1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 用数字电路的基础器件(比如74LS161计数器和76LS138译码器)可以设计什么实验电路?

用数字电路的基础器件(比如74LS161计数器和76LS138译码器)可以设计什么实验电路?

以前做实验的时候有把161和138连起来用过,设计红绿灯太简单了,有稍微难一点儿的吗? yfg31年前1

yfg31年前1 -

MPMan2k 共回答了15个问题

MPMan2k 共回答了15个问题 |采纳率100%你可以设计一个倒计时的电路呀,比如说,一上电就显示100,然后,开始倒计时,到0就停下来.这就会让你用到好多以前学过的东西了.1年前查看全部

- 急求用74ls161设计24进制计数器,有电路图更好

226789xiao1年前1

226789xiao1年前1 -

linpo15851 共回答了14个问题

linpo15851 共回答了14个问题 |采纳率92.9%因为是手机,电路图没法给,我可以给你个方案.

74ls161是异步置数同步清零十六进制计数器,构成24进制计数器有两种方法:

1.异步置数法.因为是异步,所以不用等待时钟信号就可以直接置数,构成24进制计数器的话,需要两块芯片级联,第一块计数16次后进位一次,然后第二片计数1次,当第一片计数8次与第二片计数1次后就是计数24次,此时通过门电路译出置数信号给置数端就行.

2.同步清零法.原理同置数法,只是它是同步清零,需要等待时钟信号一起作用来清零,所以在第一片计数7次与第二片计数1次后就是23次计数,此时译出清零信号,然后再等待一个时钟信号,此时计数24次,又刚好完成清零.

有不懂的地方随时回复我.

希望我的回答能帮助到你.1年前查看全部

- 74LS161的清零和预置数情况分别为( )。

74LS161的清零和预置数情况分别为( )。

A.同步清零同步预置数 B. 同步清零异步预置数

C. 异步清零同步预置数 D. 异步清零异步预置数

半山小孩1年前1

半山小孩1年前1 -

jianyili 共回答了17个问题

jianyili 共回答了17个问题 |采纳率94.1%C. 异步清零同步预置数1年前查看全部

- 如何用与非门和74LS161设计一个60进制计数器?

czhilong1年前1

czhilong1年前1 -

Bluesky0125 共回答了22个问题

Bluesky0125 共回答了22个问题 |采纳率90.9%161是模16的.一片没法弄吧~

一般用390芯片,可以实现100以内任意模值计数器

60 ==0110 0000

将第二个,第三个输出用与非门实现清01年前查看全部

- 怎样用74ls161设计一个24进制的计数器

千签难解1年前1

千签难解1年前1 -

leiber515 共回答了11个问题

leiber515 共回答了11个问题 |采纳率100%LIBRARY Ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY count24 ISPORT(en,clk: IN STD_LOGIC; co : OUT STD_LOGIC; clr_l :IN STD_LOGIC; --清零端...1年前查看全部

- 74ls161计数器计数无规律555构成的多谢振荡器,R1 = 1k~300k,R2 = 1k,电解电容C=10uF.计

74ls161计数器计数无规律

555构成的多谢振荡器,R1 = 1k~300k,R2 = 1k,电解电容C=10uF.计数时数字乱跳,有时是12.有时123,有时1234等等,有时候又是正常的16进制,把161改成160就能正常的从0计数到9. HOPEWELL198771年前1

HOPEWELL198771年前1 -

tycoms 共回答了14个问题

tycoms 共回答了14个问题 |采纳率85.7%161是二进制计数器,基于161的十进制计数器是改装的,160就是原装十进制计数器.所以用161制作的十进制计数器,在抗干扰等方面肯定比不上160原装十进制计数器.1年前查看全部

- 5V直流电源的电容的大小如何选择?具体的计算方法?该电源用于数字时钟(74LS161芯片设计)

hxlyh1年前1

hxlyh1年前1 -

lovesin 共回答了16个问题

lovesin 共回答了16个问题 |采纳率100%滤波电容的选择须要考虑二个方面,一是电容的耐压值选择,二是电容容量的选择.

电容耐压值:考虑到交流电的电压峰值和电容的安全使用系数,一般耐压值选大于2倍的交流电压值.

电容容量:依据电源的额定电流值和电容充电系数,我们就根据下式取值.

C=I*10^4/U (UF)

I——额定电流

U——电源电压

仅供参考, 福建省柘荣县华源动力设备有限公司1年前查看全部

- 急求用74ls161设计24进制计数器,有电路图更好,在线等答案,谢了

xiaokunvivi_61年前1

xiaokunvivi_61年前1 -

sdfhjdfjhdfjk 共回答了22个问题

sdfhjdfjhdfjk 共回答了22个问题 |采纳率86.4%1年前查看全部

- 数字电路问题.如何使用 预置数法 使74LS161构成二十四进制计数器

远方CAPTAIN1年前0

远方CAPTAIN1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 用4位2进制74LS161的芯片设计模为12的加法计数器?

bluesky61年前0

bluesky61年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 74LS161中RCO端是什么?

趟趟1年前1

趟趟1年前1 -

zw6603576 共回答了10个问题

zw6603576 共回答了10个问题 |采纳率90%进位信号.当qa、qb、qc、qd都为1且使能端enp、ent为1时,输出为1,否则输出为0.通常在计数器的级联时使用,连接到下一级161的clk(异步方式)或ent(同步方式),制成模更大的计数器1年前查看全部

- 集成电路74LS161是什么计数器

集成电路74LS161是什么计数器

、集成计数器74LS161是( )计数器。

A、二进制同步可预置 B、二进制异步可预置

C、二进制同步可清零 D、二进制异步可清零

qingwupiaoyang1年前1

qingwupiaoyang1年前1 -

winterzhl 共回答了18个问题

winterzhl 共回答了18个问题 |采纳率77.8%集成计数器74LS161是(A)计数器.1年前查看全部

- 如何用74ls161和与非门设计四进制计数器.

如何用74ls161和与非门设计四进制计数器.

最好画出设计的四进制计数器的线路图(也可以用纯文字说明);请说明设计思路. 冉冉的笑1年前0

冉冉的笑1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 数字电路技术基础 习题 五、 分析图5所示由 74LS161 构成的电路。(1) 画出完整的状态转换图;(2) 画出 Q

数字电路技术基础 习题 五、 分析图5所示由 74LS161 构成的电路。(1) 画出完整的状态转换图;(2) 画出 Qd

分析图 T5.11 所示由 74LS161 构成的电路。

(1) 画出完整的状态转换图;

(2) 画出 Qd 相对于 CP 的波形,说明是几分频, Qd 的占空比是多少。

世界第一炒作王1年前1

世界第一炒作王1年前1 -

qthbatghq 共回答了20个问题

qthbatghq 共回答了20个问题 |采纳率90%(1)0100, 0101, 0110, 0111, 1000,5种状态循环。

(2)Qd初始值为0,在第5个CP上升沿变为1,宽度一个时钟周期,5分频,

占空比20%。1年前查看全部

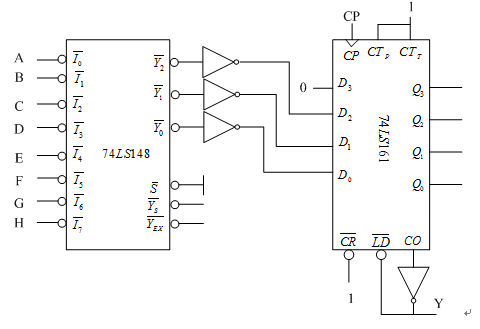

- 74LS148和74LS161构成的逻辑电路如图所示,若只有H为低,输出Y端的脉冲频率为多少.

74LS148和74LS161构成的逻辑电路如图所示,若只有H为低,输出Y端的脉冲频率为多少.

编码器74LS148和同步二进制计数器74LS161构成的逻辑电路如图T4所示,当输入控制信号A、B、C、D、E、F、G、H分别为低电平,并假定输入时钟信号频率位10KHz时,输出Y端的脉冲频率为多少.(要求写出分析过程)74LS148和74LS161功能表分别如表T4-1和T4-2所示.

只用解H为低或者A为低就行了.

题图如下:

我爱傻马马241年前1

我爱傻马马241年前1 -

y7769459 共回答了19个问题

y7769459 共回答了19个问题 |采纳率100%A-H全为低电平有效,所以低电平输入时,Y2,Y1,Y0,为反码输出000,经过反相器后,D2,D1,D0=111,所以161芯片计数初始值为D3,D2,D1,D0=0111,为十进制的7,计数周期为1111-0111+1=1001是十进制的9,计数周期为9,161芯片置数端LD是同步置数.估对输入脉冲完成9分频操作,y输出为10khz/91年前查看全部

大家在问

- 1别忘了把这件事告诉吉姆翻译成英文

- 2我想要下列句子的英文翻译,拜托,不要太难,要准确。快一点。追加哦

- 3The English story is wasy for me to read.There are only____

- 4力学 关于机械效率 最后一个填变大 但为什么啊啊 求原因!

- 5泪眼看花花不语,乱红飞过秋千去.

- 6根据课文内容回答问题。

- 7C原子的最外层电子排布为nsˇnnpˇm,其某一激发态可使这两个亚层的每一个轨道都处于充满状态,1个C原子与2个D原子结

- 8求哪位高人给画画y=x^2/3的图像

- 9为什么天气冷会很容易产生静电呢?

- 10don't know where I will go for my holiday next week.同义句I don

- 11如图,在△ABC中,BE⊥AC于点E,CF⊥AB于点F,M为BC的中点

- 12current initiatives and recommendations 怎么翻译比较好

- 13一英制指数等于多少一公制指数

- 14一点疑惑:one that may take place over time,not overnight.

- 15简便计算11*26*49*48除以(13*7*166*33)=?