真值表(大一的数字电子技术)一个对四个逻辑变量进行判断的逻辑电路,当四变量中有奇数个1出现时,输出为1.其他情况,输出为

wxyz1112022-10-04 11:39:541条回答

wxyz1112022-10-04 11:39:541条回答一个对四个逻辑变量进行判断的逻辑电路,当四变量中有奇数个1出现时,输出为1.其他情况,输出为0.列出该电路的真值表,写出输出表达式.

已提交,审核后显示!提交回复

共1条回复

198810131234 共回答了20个问题

198810131234 共回答了20个问题 |采纳率80%- 好久没接触数字,答案仅供参考,给张卡诺图:

00 01 11 10

00 0 1 0 1

01 1 0 1 0

11 0 1 0 1

10 1 0 1 0

可以看到,这并不满足化简条件,一个一个列出来:

这里我用(A)代表A的非

F=A(B)(C)(D)+(A)B(C)(D)+(A)(B)C(D)+(A)(B)(C)D+------,不给你列完了,至于真值表,从0000写道1111就行,这是很基本的,不过A,B,C,D以及F要标明了 - 1年前

相关推荐

- 数字逻辑 8421转余3码我们数字逻辑中有个题是这样的要求把8421码转换成 要具体的 方法我知道 我需要的是 真值表之

数字逻辑 8421转余3码

我们数字逻辑中有个题是这样的

要求把8421码转换成 要具体的

方法我知道 我需要的是 真值表之类的 零K1年前1

零K1年前1 -

floatdream 共回答了15个问题

floatdream 共回答了15个问题 |采纳率86.7%余三码(余3码)【计算机】是由8421码加上0011形成的一种无权码,由于它的每个字符编码比相应的8421码多3,故称为余三码.BCD码的一种.

0-0011,1-0100,2-0101,3-0110,4-0111,5-1000,6-1001,7-1010,8-1011,9-1100.

余三码是一种对9的自补代码,因而可给运算带来方便.其次,在将两个余三码表示的十进制数相加时,能正确产生进位信号,但对“和”必须修正.修正的方法是:如果有进位,则结果加3;如果无进位,则结果减3.

如,(526)10=(0101 0010 0110)8421码=

(0101+0011 0010+0011 0110+0011)余3码=

(1000 0101 1001)余3码1年前查看全部

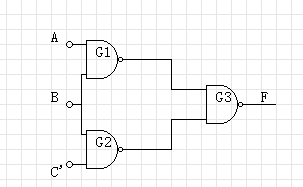

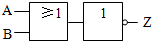

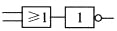

- 如图为一逻辑电路,根据电路图完成它的真值表。其输出端从上到下排列的结果正确的是

如图为一逻辑电路,根据电路图完成它的真值表。其输出端从上到下排列的结果正确的是

[ ]

A.0 0 1 0

B.0 0 1 1

C.1 0 1 0

D.0 0 0 1 lusenwang1年前1

lusenwang1年前1 -

佳春秋1023 共回答了18个问题

佳春秋1023 共回答了18个问题 |采纳率77.8%D1年前查看全部

- 4变量逻辑函数的真值表,应该有多少行?A、2; B、4; C、8; D、16

葛藤1年前2

葛藤1年前2 -

逍遥快乐 共回答了19个问题

逍遥快乐 共回答了19个问题 |采纳率89.5%D,161年前查看全部

- 用真值表判定p→┑q与┑pv┑q是否等值?

aa1251年前1

aa1251年前1 -

锅炉工 共回答了18个问题

锅炉工 共回答了18个问题 |采纳率94.4%p q ┑p ┑q p→┑q ┑pv┑q

0 0 1 1 1 1

0 1 1 0 1 1

1 0 0 1 1 1

1 1 0 0 0 0

所以:p→┑q与┑pv┑q等值1年前查看全部

- 用真值表法判定( ┑ p∨q ) ∧ ┑ p → q 是否是重言式.有真值表,

小华花1年前1

小华花1年前1 -

醉空楼 共回答了10个问题

醉空楼 共回答了10个问题 |采纳率90%真值表法判定( ┑ p∨q ) ∧ ┑ p → q

px05qx05┑ px05┑ p∨qx05(┑p∨q)∧┑px05(┑ p∨q)∧┑p→q

Tx05Tx05Fx05Tx05 Fx05 T

Tx05Fx05Fx05Fx05 Fx05 T

Fx05Tx05Tx05Tx05 Tx05 T

Fx05Fx05Tx05Tx05 T x05 F

从上图看;最后得出结论( ┑ p∨q ) ∧ ┑ p → q是重言式

(同为作业苦恼的人送上,不知最后一题答案知晓?)1年前查看全部

- 在如图所示的逻辑电路中,其真值表的“输出”这一列数据从上到下依次为( ) 输入 输出 0 0 0 1 &

在如图所示的逻辑电路中,其真值表的“输出”这一列数据从上到下依次为( )

在如图所示的逻辑电路中,其真值表的“输出”这一列数据从上到下依次为( ) 输入 输出 0 0 0 1 1 0 1 1

A.0,0,0,1

B.1,0,0,0

C.0,1,0,1

D.1,0,1,0 小小小呆熊1年前1

小小小呆熊1年前1 -

水中泪6666 共回答了24个问题

水中泪6666 共回答了24个问题 |采纳率91.7%解题思路:图示电路为或非门,当AB输入经或门输出再经非门输出.当AB输入00经或门输出0再经非门输出1,当AB输入01经或门输出1再经非门输出0;当AB输入10经或门输出1再经非门输出0;当AB输入11经或门输出1再经非门输出0;故输出1,0,0,0,故B正确

故选B点评:

本题考点: 简单的逻辑电路.

考点点评: 考查了基本门电路的基本逻辑输入输出关系,理解组合门的输入输出.1年前查看全部

- 根据真值表写出逻辑函数的原理是什么?不是方法,方法我知道,为什么把逻辑函数取1的乘积相加就得到逻辑函数,两者是怎样联系起

根据真值表写出逻辑函数的原理是什么?不是方法,方法我知道,为什么把逻辑函数取1的乘积相加就得到逻辑函数,两者是怎样联系起来的

映雪醉月1年前1

映雪醉月1年前1 -

wangkun200408 共回答了17个问题

wangkun200408 共回答了17个问题 |采纳率94.1%上述概念都是【逻辑代数】中的内容.【逻辑代数】是【数学】与【逻辑学】相结合的产物.【逻辑代数】中的内容,都可以在其中找到原始的解释:

1、数学解释:

【逻辑函数】是数学函数的一种,表示的是【逻辑变量】——取值范围为{0,1}的变量——间的对应关系.这种关系是通过【逻辑运算】建立的,所以,【逻辑函数】的一切性质,都是由【逻辑变量】和【逻辑运算】决定的.先说说【逻辑运算】:

①:【与——逻辑乘】:Y=X1·X2·……·Xk;(k个逻辑变量连乘)

表示:Y=1,当且仅当 X1、X2、……、Xk【全部等于1】;

②:【或——逻辑加】:Y=X1+X2+……+Xk;(k个逻辑变量连加)

表示:Y=1,当且仅当 X1、X2、……、Xk【至少一个等于1】;

③:【非——逻辑非】:Y=X′;(我用X′表示:X的非)

表示:Y=1,当且仅当 X【等于0】;

逻辑函数的通用表达式为:

Y=f(X1,X2,……,Xk);——k元逻辑函数;

在【真值表】中,k元逻辑函数必然恰好具有:2^k行.我们用:

v=(x1,x2,……,xk)

来表示真值表某一行中全部自变量的【赋值组合】. 那么该行对应的函数值可记作:

Y=f(v);

我们知道,自变量的【赋值组合】唯一确定了Y的取值.根据每行中Y的不同取值(0或1),可将每行所对应的【赋值组合】分为两组:

A组:Y=1;记作:A={a1,a2,……,am};——设共有m行;

B组:Y=0;记作:B={b1,b2,……,bn};——设共有n行;

显然:m+n=2^k;并且:

Y=f(a1)=f(a2)=……=f(am)=1;

Y=f(b1)=f(b2)=……=f(bn)=0;

另外,因为每个【赋值组合】都要取遍所有自变量,那么,每行的【赋值组合】必然可以对应一个【最小项】,构造规则如下:

①:如果Xi=1;则使用【正变量】——Xi;

②:如果Xi=0;则使用【反变量】——Xi′;

根据【逻辑乘】和【逻辑非】的运算性质,可知:使用此方法构造最小项,必然具有以下性质:

【1】可以构造出k个变量的全部【最小项】,它们恰好分别对应【真值表】中的每一行;

【2】每个【赋值组合】,恰好也是【唯一的】可以使相应【最小项】等于1的【赋值组合】;

根据【2】所确定的【赋值组合】与【最小项】间的一一对应关系,我们将该【逻辑函数】的所有的【最小项】也分为两组:

M={A1,A2,……,Am};

N={B1,B2,……,Bn};

其中的每个元素都是一个个的【最小项】;并且,我们规定M、N中元素的下标,与A、B中所对应的元素的下标是一致的.

现在,我们可以确定这样一种关系了:

Y=f(v)=1;

当且仅当:v∈A;

当且仅当:存在ai=v∈A;(i是一个不确定的下标)

当且仅当:Ai=1;显然:Ai∈M;

当且仅当:所有Aj=Bl=0;其中:Aj∈M且j≠i;Bl∈N;(j和l都是下标)

这也就是说:

Y=1;当且仅当:M中【至少(事实上,也是恰好)有1个】最小项也等于1.

再根据【逻辑加】的运算性质,可知,Y必然满足以下等式:

Y=A1+A2+……Am;

这,就是该【逻辑函数】的【标准与或式】.也就是根据【真值表】直接写出来的【逻辑表达式】.1年前查看全部

- 下面哪一个是“或”门的真值表?( ) A.

下面哪一个是“或”门的真值表?( ) A.

B.

C.

D.

Tokura1年前1

Tokura1年前1 -

飞天鱼呀 共回答了13个问题

飞天鱼呀 共回答了13个问题 |采纳率84.6%根据或门的特点知,当输入有1时,输出为1,当输入为0,0时,输出为0.故D正确,A、B、C错误.

故选D.1年前查看全部

- 组合逻辑电路的分析和设计使用的主要工具是什么?是真值表吗?

水石141年前1

水石141年前1 -

winlove1314 共回答了19个问题

winlove1314 共回答了19个问题 |采纳率94.7%分析和设计用的方法不同,分析可以从逻辑图的入端往输出端写表达式,并化简,然后列真值表,分析逻辑功能;设计从真值表开始,由题目要求列真值表,写表达式,再化简画逻辑图.1年前查看全部

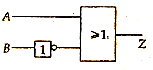

- (2006•黄浦区模拟)如图是一个简单的组合逻辑电路,完成其真值表.

(2006•黄浦区模拟)如图是一个简单的组合逻辑电路,完成其真值表.

(2006•黄浦区模拟)如图是一个简单的组合逻辑电路,完成其真值表.

A B Z 0 0 ______ 0 1 ______ 1 0 ______ 1 1 ______  珊霞1年前1

珊霞1年前1 -

lsxz991 共回答了18个问题

lsxz991 共回答了18个问题 |采纳率83.3%解题思路:非门的特点是输入状态与输出状态完全相反;或门的特点是只要有一个条件满足,该事件就会发生.对于非门,输入0,输出1,输入1,输出0.对于或门,只要有一端输入为1,输出为1.所以A、B两端输入为0,0,则输出为1;输入为0,1,输出为0;输入为1,0,输出为1;输入为1,1,输出为1.

故本题答案为:

A B Z

0 0 1

0 1 0

1 0 1

1 1 1点评:

本题考点: 简单的逻辑电路.

考点点评: 解决本题的关键掌握非门和或门的特点,非门的特点是输入状态与输出状态完全相反;或门的特点是只要有一个条件满足,该事件就会发生.1年前查看全部

- 逻辑电路如下图所示,试分析其逻辑功能.要求写出逻辑表达式,画出真值表.

werner10201年前1

werner10201年前1 -

274月明 共回答了24个问题

274月明 共回答了24个问题 |采纳率79.2%X=(A'+B)' =AB' Z=(A+B')' =A'B Y=((A'+B)'+(A+B')')'=AB'+A'B

A B X Y Z

0 0 0 0 0

0 1 0 1 1

1 0 1 0 1

1 1 0 0 01年前查看全部

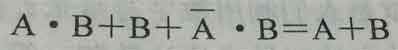

- 逻辑电路的真值表证明题目 会的大侠帮帮忙

逻辑电路的真值表证明题目 会的大侠帮帮忙

证明

天堂路灯1年前1

天堂路灯1年前1 -

li740208 共回答了19个问题

li740208 共回答了19个问题 |采纳率100%F=AB+B+A'B=A+B

A B F = AB + B + A'B A+B

0 0 0 0 0 0 0

0 1 1 0 1 1 1

1 0 0 0 0 0 1

1 1 1 1 1 0 1

从真值表第三列(F) 与第七列(A+B) 不相等,看出题目中的等式是错误的!

正确的应当是:AB+B+A'B=B(A+1)+B(1+A')=B

即:AB + B + A'B = B ≠ A+B .1年前查看全部

- 一逻辑电路的输出P和输入A、B的真值表如下表,此逻辑电路是______电路.

一逻辑电路的输出P和输入A、B的真值表如下表,此逻辑电路是______电路.

真值表

A B P 0 0 0 0 1 1 1 0 1 1 1 1  去TMD爱情1年前1

去TMD爱情1年前1 -

成信痞子 共回答了17个问题

成信痞子 共回答了17个问题 |采纳率82.4%解题思路:非门的特点是输入状态和输出状态完全相反,与门的特点是当所有条件都满足,事件才能发生;或门的特点是当某个条件满足,事件就能发生.根据门电路的特点进行判断.A段输入为0011;B端输入为0101;P端输出为0111;

两个输入端只要有一个输入1,输出即为1,故是或门电路;

故答案为:或门.点评:

本题考点: 简单的逻辑电路.

考点点评: 解决本题的关键知道各种门电路的特点,对照真值表判断即可.1年前查看全部

- 用真值表方法证明是否为重言式(p→q)∧(r→q)∧(p∨q)→q

荆卫玲1年前1

荆卫玲1年前1 -

测测大师 共回答了11个问题

测测大师 共回答了11个问题 |采纳率90.9%p q p→q r q r->q (p→q)∧(r→q) p∨q (p→q)∧(r→q) ^(p∨q) 0 1 1 0 1 1 1 1 1 0 0 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 0 1 1 1 1 1 1 1 1 1 (p→q)∧(r→q) ^(p∨q) q (p→q)∧(r→q)∧(p∨q)→q 1 1 1 0 0 1 0 0 1 1 1 1 还有一种情况自己想着办 ..1年前查看全部

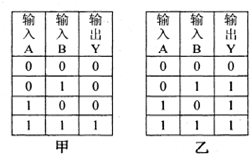

- 如图所示是两个门电路的真值表,下列判断正确的是( )

如图所示是两个门电路的真值表,下列判断正确的是( )

如图所示是两个门电路的真值表,下列判断正确的是( )

A.甲表对应的是“与”门电路

B.乙表对应的是“与”门电路

C.甲表对应的是“或”门电路

D.乙表对应的是“非”门电路 鱼缸里的晶鱼1年前1

鱼缸里的晶鱼1年前1 -

sjapzjp_spoe 共回答了24个问题

sjapzjp_spoe 共回答了24个问题 |采纳率87.5%解题思路:与逻辑关系是输入都为高电势输出才为高电势;

或逻辑关系是输入中有一个为高电势则输出为高电势;

非逻辑关系是输入为高电势则输出为低电势;甲图中输入0 0 输出为0,输入0 1输出为0,输入1 0 输出为0,输入1 1 输出为1,即输入端都为高电势输出才为高电势,故甲为“与”门电路;

乙图中输入0 0 输出为0,输入0 1输出为1,输入1 0输出为1,输入1 1 输出为1,即输入中有一个为高电势则输出为高电势,故乙为“或”们电路;

故A是正确的BCD错误.

故选:A.点评:

本题考点: 简单的逻辑电路.

考点点评: 考查了真值表的分析逻辑关系,判断门电路.1年前查看全部

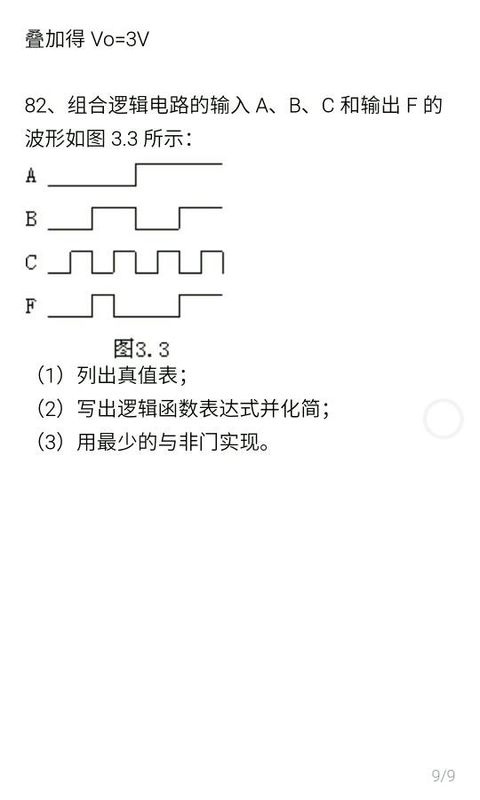

- 组合逻辑电路的输入A、B、C和输出F的波形如图3.3所示: (1)列出真值表; (2)写出逻辑函数

组合逻辑电路的输入A、B、C和输出F的波形如图3.3所示: (1)列出真值表; (2)写出逻辑函数

组合逻辑电路的输入A、B、C和输出F的波形如图3.3所示:

(1)列出真值表;

(2)写出逻辑函数表达式并化简;

(3)用最少的与非门实现.

真实的我5201年前1

真实的我5201年前1 -

小镇无忧妹 共回答了22个问题

小镇无忧妹 共回答了22个问题 |采纳率90.9%1年前查看全部

- 某逻辑电路真值表如下表所示,其函数F的表达式为

某逻辑电路真值表如下表所示,其函数F的表达式为

A、F= 非B B、F=A C、F=非A D、F=B

A B F

0 0 0

0 1 0

1 0 1

1 1 1 寻找对的另一半1年前1

寻找对的另一半1年前1 -

wralysdm 共回答了16个问题

wralysdm 共回答了16个问题 |采纳率93.8%F=AB'+AB=A(B'+B)=A

选择B1年前查看全部

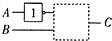

- 如图是两个简单的门电路组成的逻辑电路及对应的真值表,则电路中虚线框内的门电路是______门,真值表中的x值为_____

如图是两个简单的门电路组成的逻辑电路及对应的真值表,则电路中虚线框内的门电路是______门,真值表中的x值为______.

如图是两个简单的门电路组成的逻辑电路及对应的真值表,则电路中虚线框内的门电路是______门,真值表中的x值为______.

输出 输入 A B C 0 0 1 0 1 x 1 0 0 1 1 1  孤独的永远1年前1

孤独的永远1年前1 -

爱我所爱是我啊 共回答了22个问题

爱我所爱是我啊 共回答了22个问题 |采纳率90.9%解题思路:非门的特点是输入状态和输出状态完全相反,与门的特点是当所有条件都满足,事件才能发生;或门的特点是当某个条件满足,事件就能发生.根据门电路的特点进行判断.A段输入为0011;经过非门后变为1100.

B端输入为0101;

当虚框输入有一个高电位1时,输出就为1,故是或门电路;

故答案为:或,1.点评:

本题考点: 简单的逻辑电路.

考点点评: 解决本题的关键知道各种门电路的特点,并能灵活运用.1年前查看全部

- 如图是两个门电路的真值表,下列判断正确的是( )

如图是两个门电路的真值表,下列判断正确的是( )

甲表

乙表输入

A输入

B输出

Y0 0 0 0 1 0 1 0 0 1 1 1 输入

A输入

B

输出

Y0 0 0 0 1 1 1 0 1 1 1 1

A.甲表对应的是“与”门电路

B.乙表对应的是“与”门电路

C.甲表对应的是“或”门电路

D.乙表对应的是“非”门电路 Ainuer1年前1

Ainuer1年前1 -

孔雀Pei 共回答了20个问题

孔雀Pei 共回答了20个问题 |采纳率85%解题思路:根据逻辑电路的逻辑关系解答即可.A、C、甲表中,当输入端A、B的输入都是1时,输出端才是1,即AB的条件同时满足,输出才是高电平.故该逻辑电路是“与”逻辑关系.故A正确,C错误;

B、D、乙输入端A、B的输入有一个是1时,输出端是1,即AB的条件满足一个,输出就是高电平.故该逻辑电路是“或”逻辑关系.故BD错误.

故选:A点评:

本题考点: 简单的逻辑电路.

考点点评: 该题考查简单的逻辑关系是的真值关系,只要记住即可正确解答.基础题目.1年前查看全部

- 一、用真值表法判定下列式子是否重言式.

一、用真值表法判定下列式子是否重言式.

(p∧(q∨r))→((p∧q)∨(p∧r))

x05

二、***局审理一起盗窃案,已知:

(1)甲或乙是盗窃犯.

(2)若甲是盗窃犯,则作案时间不可能发生在午夜前.

(3)若乙的证词正确,则在午夜时屋里灯光未灭.

(4)若乙的证词不正确,则作案时间发生在午夜前.

(5)午夜时屋里灯光灭了.

问:谁是盗窃犯?写出逻辑推导过程.

三、某公司准备选拔一个销售经理,甲、乙、丙三位董事经过充分考虑后提出意见如下:

甲:要么聘用李先生,要么聘用王先生.

乙:如果不聘用李先生,那么也不要聘用王先生.

丙:如果不聘用王先生,那么就聘用李先生.

如何选择一个方案,同时满足三位董事的意见?写出逻辑推导过程. qinchong1年前1

qinchong1年前1 -

美丽从这里开始 共回答了17个问题

美丽从这里开始 共回答了17个问题 |采纳率100%1(p∧(q∨r))→((p∧q)∨(p∧r))是重言式

0 0 0 0 0 1 0 0 0 0 0 0 0

0 0 0 1 1 1 0 0 0 0 0 0 1

0 0 1 1 0 1 0 0 1 1 0 0 0

1 0 0 0 0 1 1 0 0 0 1 0 0

1 1 0 1 1 1 1 0 0 1 1 1 1

1 1 1 1 0 1 1 1 1 1 1 0 0

1 1 1 1 1 1 1 1 1 1 1 1 1

2.

(1)甲or乙

(2)甲→非前

(3)正→未灭

(4)非正→前

(5)灭

(6) 非正 (3,5)→-

(7) 前 (4,6)→-

(8) 非甲 (2,7)→-

(9) 乙 (1,8)or-

答:乙是盗窃犯.

2.

李 王 非李 非王 李→非王 非李→非王 非王→李

0 0 1 1 1 1 0

0 1 1 0 1 0 1

1 0 0 1 1 1 1

1 1 0 0 0 1 1

答:由上面的真值表可见,当李去王不去时,符合甲乙丙三个懂事的要求.1年前查看全部

- 输入 输出 0 0 1 0 1 1 1 0 1 1 1 0 表中是某逻辑电路的真值表,该电路是( ) A.

表中是某逻辑电路的真值表,该电路是( )输入 输出 0 0 1 0 1 1 1 0 1 1 1 0 A.

B.

C.

D.

johnsonvan1年前1

johnsonvan1年前1 -

haleelife 共回答了19个问题

haleelife 共回答了19个问题 |采纳率73.7%A、将第一组真值表表中数据代入“或”门,输出端应为0.故A错误.

B、将第一组真值表表中数据代入“与”门,输出端应为0.故B错误.

C、将第二组真值表表中数据代入“或非”门,输出端应为0.故C错误.

D、将各组真值表中的数据代入“与非”门,输出端都正确.故D正确.

故选D.1年前查看全部

- 试用门电路设计一个三变量判奇电路,要求列出其真值表,写出逻辑表达式.

threefourtwelve1年前1

threefourtwelve1年前1 -

phgxh 共回答了22个问题

phgxh 共回答了22个问题 |采纳率90.9%1年前查看全部

- 什么是真值表?

nimonekua1年前1

nimonekua1年前1 -

xlhzql 共回答了15个问题

xlhzql 共回答了15个问题 |采纳率93.3%列出命题公式真假值的表.通常以 1表示真,0 表示假.命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法:x0d即::当P为假时,P为真;当P为真时,P为假.x0d真值表是在逻辑中使用的一类数学表,用来确定一个表达式是否为真或有效. (表达式可以是论证;就是说,表达式的合取1年前查看全部

- 作出下列命题的真值表:并非“室内很冷或很乱”也不是“室外暖和且室内太脏”.

pmy11041年前1

pmy11041年前1 -

雨滴RianDrop 共回答了14个问题

雨滴RianDrop 共回答了14个问题 |采纳率100%设X表示“室内很冷”,Y表示“室外暖和”,Z表示“室内很乱”,W为“室内太脏”

所以输出Q=(X+Z)的非 且 (YW)的非

真值表只有当X=Y=Z=W=0时,Q才取1,其他15中情况Q都取0(字数有限,无法画真值表)1年前查看全部

- (2013•崇明县一模)右面是某最简单逻辑电路的真值表,根据这个真值表可以判断此逻辑电路使用的门电路和表中的“X”的取值

(2013•崇明县一模)右面是某最简单逻辑电路的真值表,根据这个真值表可以判断此逻辑电路使用的门电路和表中的“X”的取值分别为( )

输入 输出 A B A 0 0 0 0 1 X 1 0 1 1 1 1

A.或门,X=1

B.与门,X=1

C.非门,X=0

D.或门,X=0 我可爱的小精灵1年前1

我可爱的小精灵1年前1 -

夺烟寻淡 共回答了22个问题

夺烟寻淡 共回答了22个问题 |采纳率86.4%解题思路:会根据逻辑电路的真值表推断逻辑关系、逻辑门电路.由逻辑电路的真值表可得,该逻辑关系为或逻辑关系,对应的门电路为或门电路,x=1,故A正确

故选A点评:

本题考点: 简单的逻辑电路.

考点点评: 考查了由逻辑门电路的真值表推断逻辑关系、逻辑门电路.1年前查看全部

- 逻辑试题 难 急求1.列出下列AB两个判断形式的真值表,并根据真值表回答A是否是B的必要条件. A:p←→q B:q→「

逻辑试题 难 急求

1.列出下列AB两个判断形式的真值表,并根据真值表回答A是否是B的必要条件.

A:p←→q B:q→「p (「 这个符号倒下来!我不会打.)

2.列出下列ABC三个判断的真值表,并根据真值表回答:当ABC中只有一个真话时,哪一句是真?甲是否去开会?乙是否去上学?

A:如果乙去上学,那么甲去开会

B:并非要么甲去开会要么乙去上学

C;甲不去开会或乙不去上学

分析 推理过程 28wentian1年前2

28wentian1年前2 -

enmic1 共回答了20个问题

enmic1 共回答了20个问题 |采纳率90%很简单 C是真话

首先考虑A :假设A是真话,那么,乙去上学甲必然去开会,应该两者同时去.或者甲也不去,乙也不去,两者都不去.既然A是真话,那么B和C都为假话,B中要么甲去,要么乙去,意思是二者选其一,但前面加了并非,说明不一定要二者选其一,可以两人都不去,也可以两人都去.与A中产生的观点相一致.但偏偏B又是假话,所以与A相互矛盾,所以A为真话的话不符合上下逻辑,即A为假话.

再来考虑B :假设B为真话,那么,上述已分析过,可以两者都去,也可两者都不去,但A与C都为假话,同样与A不符合,既然不符合,那么便不用再来分析C,即B也为假话.

再来考虑 C:假设C为真话,甲不去或者乙不去,说明两人中肯定有一人是不去,有一人是去的,有两种情况,1甲去开会,乙不去上学 2甲不去开会,乙去上学.也就是说不能甲和乙同时去,或甲和乙都不去.A和B为假话,本来A是甲和乙同时去或同时不去,既然是假话,那么就反一下,就与C相互一致.本来B是说可以两人同时去或同时不去,也是假话,那么也反一下,也与C相互一致,那么三项表达的意思和逻辑都一致了,所以C是真话.

哎 我打的很辛苦,希望你能看得懂.1年前查看全部

- 画出一个二极管三变量“与门”电路,并写出其逻辑符号、真值表与逻辑表达式

ctyki1年前0

ctyki1年前0 -

共回答了个问题

共回答了个问题 |采纳率

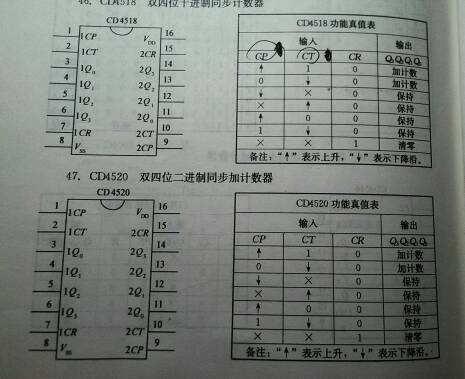

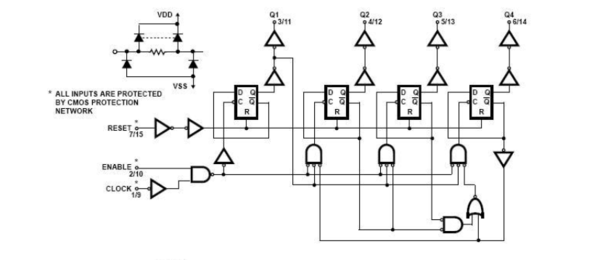

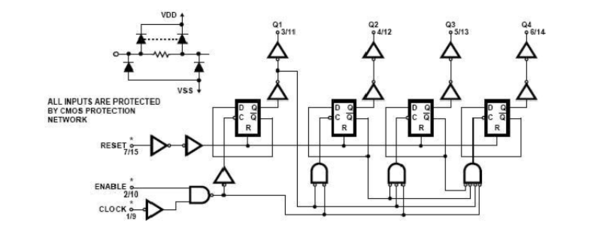

- 真值表相同的CD4520和CD4518实现的六十进制计数器从电路原理图上看有不同吗?我知道20是十六进制,18是十进制,

真值表相同的CD4520和CD4518实现的六十进制计数器从电路原理图上看有不同吗?我知道20是十六进制,18是十进制,但是我不知道这会导致电路原理图有什么不同?

werddeeer1年前1

werddeeer1年前1 -

summerxcity 共回答了16个问题

summerxcity 共回答了16个问题 |采纳率100%CD4518/CC4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示.每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发.由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”.RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数.

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次.这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态.若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数.CD4520/CC4520为二进制加计数器,由两个相同的内同步4级计数器构成.计数器级为D型触发器,具有内部可交换CP和EN线,用于在时钟上升沿或下降沿加计数.在单个单元运算中,EN输入保持高电平,且在CP上升沿进位.CR线为高电平时,计数器清零.计数器在脉动模式可级联,通过将Q3连接至下—计数器的EN输入端可实现级联,同时后者的CP输入保持低电平.

1年前查看全部

1年前查看全部

- 逻辑函数真值表确定后,描述函数功能的方法中具有唯一性的是

sq6661年前1

sq6661年前1 -

MrHood 共回答了17个问题

MrHood 共回答了17个问题 |采纳率100%最小项表达式、最大项表达式是唯一的

最简与或式,最简或与式,真实函数功能的逻辑电路都不是唯一的1年前查看全部

- 数字电路逻辑设计的一道题.题目的部分后面是画出真值表,状态图和时序图

57711年前1

57711年前1 -

sbringmouse 共回答了27个问题

sbringmouse 共回答了27个问题 |采纳率96.3%这个先写出输入方程,状态方程.根据方程列出状态表,进而写出真值表.这个过程比较多,慢慢琢磨吧!不太难.1年前查看全部

- 请问图中的真值表怎么写出相应的逻辑函数表达式?

龙换天下1年前1

龙换天下1年前1 -

burning_ice 共回答了23个问题

burning_ice 共回答了23个问题 |采纳率87%Y1=AB'C'+A'BC'+A'B'C+ABC

Y2=ABC'+AB'C+A'BC+ABC=AB+BC+AC1年前查看全部

- 在集成电路中,经常用若干基本门电路组成复合门电路,如图所示,为两个基本门电路组合的逻辑电路,根据真值表,判断虚线框内门电

在集成电路中,经常用若干基本门电路组成复合门电路,如图所示,为两个基本门电路组合的逻辑电路,根据真值表,判断虚线框内门电路类型及真值表内x的值( )

在集成电路中,经常用若干基本门电路组成复合门电路,如图所示,为两个基本门电路组合的逻辑电路,根据真值表,判断虚线框内门电路类型及真值表内x的值( )

A B 2 0 0 1 0 1 0 1 0 0 1 1 x

A.“与门”,1

B.“与门”,0

C.“或门”,0

D.“或门”,1 十二万个为什么1年前1

十二万个为什么1年前1 -

8645360354075a71 共回答了19个问题

8645360354075a71 共回答了19个问题 |采纳率84.2%当AB输入为00时,通过第一个门电路输出为0,输入为01时,输出为1,输入为10时,输出为1,知该门电路为“或”门.所以输入为11时,输出为1,再经过非门输出为0,所以x为0.

故选:C1年前查看全部

- 已知显示译码器(七段数码管)的真值表,共阴极和共阳极的显示译码器输出逻辑表达式如何求?

已知显示译码器(七段数码管)的真值表,共阴极和共阳极的显示译码器输出逻辑表达式如何求?

就是已知共阴的真值表,输出abcdefg,想求abcdefg的逻辑表达式,一般来说逻辑表达式都是把1的相加不就完了吗,但是答案写的是0的相加,我想问为什么 gg打kk1年前1

gg打kk1年前1 -

紫烟love 共回答了16个问题

紫烟love 共回答了16个问题 |采纳率75%真值表是根据共阳来算的,共阴时就取反1下

真值表是根据共阴来算的,共阳时就取反1下1年前查看全部

- 用真值表证明等式AB+A~B=(A+B~)(A~+B)那个~是A或B上的一横,我真的不懂啊!可能是打错了吧……我想问那个

用真值表证明等式

AB+A~B=(A+B~)(A~+B)

那个~是A或B上的一横,我真的不懂啊!

可能是打错了吧……我想问那个AB+A~B和(A+B~)(A~就是用逻辑关系用语言表达,我不太明白两个相乘或两个相加是什么东东? 芦荟0091年前1

芦荟0091年前1 -

暗夜Vampire 共回答了20个问题

暗夜Vampire 共回答了20个问题 |采纳率100%列出真值表:

A B AB+A~B (A+B~)(A~+B)

0 0 0 1

0 1 1 0

1 0 0 0

1 1 1 1

显然不等嘛,你是不是题打错了?

两个相乘是逻辑与,相加是逻辑或,下面是真值表:

A B AB A+B

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 1

两个数都是1时逻辑与才是1

两个数都是0时逻辑或才是01年前查看全部

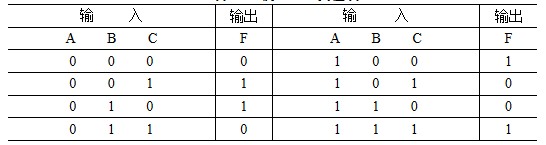

- 74LS193的真值表!请用0,1表示其真值表,

我要提问呀1年前1

我要提问呀1年前1 -

客来几人知 共回答了15个问题

客来几人知 共回答了15个问题 |采纳率86.7%1年前查看全部

- 表解题:用真值表确定 p∨q和(p∨q)之间的关系.

老虫ahhbwq1年前1

老虫ahhbwq1年前1 -

破琴 共回答了12个问题

破琴 共回答了12个问题 |采纳率100%不就是一个?

true || true = true

true || false = true

false || false = false1年前查看全部

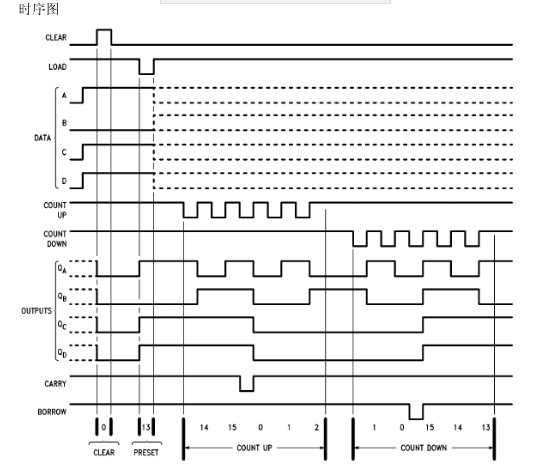

- 写出它的驱动方程、状态方程,列出状态转换真值表和状态图,画出时序波形图,说明是几进制计数器.

写出它的驱动方程、状态方程,列出状态转换真值表和状态图,画出时序波形图,说明是几进制计数器.

明上午要用! Lara 慧1年前1

Lara 慧1年前1 -

weileejiao 共回答了22个问题

weileejiao 共回答了22个问题 |采纳率90.9%1年前查看全部

- 关于逻辑涵数的真值表怎么求?例如:F1=ABC+非A非B非C的真值表?

只能吧1年前1

只能吧1年前1 -

一棵老葱 共回答了18个问题

一棵老葱 共回答了18个问题 |采纳率100%逻辑函数,函数的一种.与常见的数学函数(如线性函数、反比例函数、一元二次函数、指数函数等)相比,区别是:

(1)以上初等数学函数的自变量只有一个 x;而逻辑函数的自变量通常有很多,比如你给的例子 F1 的自变量就有 3 个:A、B、C;

(2)普通数学函数的定义域和值域通常为实数域(或它的一个子集),通常是连续的,是个无穷集合;而逻辑函数“每个自变量的取值范围”和函数的值域都只有两个元素:{真,假},它还有很多等价的表示方法:{T, F}、{0, 1};而“整个函数的定义域”则为所有自变量取值集合的“笛卡儿积”;比如你给的例子 F1 的定义域就是:

{0, 1} × {0, 1} × {0, 1}

= {, , , , , , , }

基于以上区别,两类函数的表示方法就有所不同.除了所有函数都通用的表达式方法外,普通函数通常用函数图像表示;而逻辑函数则可以用真值表来表示——因为它的定义域和值域中的元素个数都比较少,而且很有规律.

真值表作为逻辑函数的表示方法,目的就是将函数定义域中每个元素(即自变量元组)与它所对应的函数值一一列出.所以真值表的行数(R)是由自变量的个数(n)确定的:

R = 2 ^ n;

而真值表的列是由自变量列和函数值列组成的,所以列数(C)为:

C = n + 1;

当然,就像多个函数的图像可以画在同一个坐标系中一样,多个函数的真值表也可以合并为一张真值表.这时,真值表的定义域就应该是所有函数的定义域的并集.对于 m 个逻辑函数,如果它们共包含 N 个自变量,那这些函数的真值表的行数和列数分别为:

R = 2 ^ N;

C = N + m;

前面已说过,画真值表就是要建立逻辑函数定义域中每个元素与其函数值的对应关系.其过程为:

第1步:根据函数个数和自变量个数建立空表,一般是要加个表头的;——这一步相当于画坐标系;

第2步:填入定义域元素,即:填写所有自变量的取值组合;——这一步相当于标记定义域;

第3步:为每个逻辑函数,计算定义域的每个元素的函数值,并填入;——这是唯一需要计算的地方,相当于画函数图像上的每个点;

对于你的例子,F1 = ABC + A'B'C';(A' = 非A),F1 的真值表是一个 8 行(不算表头)4 列的表格.前两步就不说了,唯一有难度的地方就是函数值的计算.比如,当自变量为时,函数值为:

F1 = 0 · 0 · 0 + 0' · 0' · 0' = 0 + 1 · 1 · 1 = 0 + 1 = 1;

其他的函数值可自行求解.

补充:关于真值表的制作,最难也最麻烦的地方就是函数值的计算.不过由于逻辑函数的特殊性,使得它的表达式和真值表直接有着很有规律的联系,我们可以直接从函数表达式得出真值表中的函数值列.只不过需要将表达式转化为标准形式,即:积之和式(又叫析取范式).从逻辑函数的积之和式,可以直接看出真值表中 “函数值为 1 的行”,剩下的行的函数值自然就是 0 了.

分析:不管是表达式还是真值表,都是要表示自变量与函数值直接的取值关系.对于积之和式,只要它的任何一个“与项”的取值为 1,函数值就为 1.所以:使得任何一个“与项”为 1 的“自变量取值组合”,必然使得整个函数取值为 1,这样的自变量组必然对应真值表中函数值为 1 的行;反之,不能使任何一个与项为 1(即:使得每个与项都为 0)的自变量组,必然使整个函数的值为 0,这样的自变量组必然对应真值表中函数值为 0 的行.

每个“与项”(用 p 表示)都会有一个或多个使它取值为 1 的自变量组,它(们)构成一个集合:P.我们只要依次分析每个“与项”(p1、p2、p3…),就可以得到相应的自变量组的集合:P1、P2、P3….而这些集合的并集,就是所有函数值为 1 的自变量组构成的集合.通过例子说明:

例:F = A + A'B;

(1)p1 = A:当 A = 1时,无论B、C取何值,该项的结果为 1;而 A = 0时,该项也必为0;所以,它所对应的自变量组集合为:P1 = {, };

(2)p2 = A'B:当且仅当 A = 0、B = 1时,该项 = 1;P2 = {};

现在,规律很明显了:对于每个与项,分析函数的每个变量:当变量以“原变量”形式出现时,记为 1;当以“反变量”形式出现时,记为 0;当变量不出现时,应当考虑它(们)所有的 0、1 组合.由此就能得到使该与项为 1 的自变量组(或自变量组的集合).

对于你给的例子:F1 = ABC + A'B'C';

(1)p1 = ABC:P1 = {};

(2)p2 = A'B'C':P2 = {};

所以,在F1的真值表中,就只有和两行的函数值为1,其他行为0;1年前查看全部

- 离散数学化简命题公式的问题这个命题公式使用真值表判断为永真式,请问如何化简?

雪落飞花1年前1

雪落飞花1年前1 -

就怕查体 共回答了16个问题

就怕查体 共回答了16个问题 |采纳率93.8%化简为主析取范式·1年前查看全部

- 电路如图,试写出Y的逻辑表达式,并列出真值表

Google测试员34121年前1

Google测试员34121年前1 -

1中老年妇女ff 共回答了22个问题

1中老年妇女ff 共回答了22个问题 |采纳率86.4%Y=!(!(AC)!(AB)!(BC))=!(!(AC)!(AB))+BC=AC+AB+BC然后你变换下 当A=0时表达式Y=A(B+C)+BC 然后把bc按照1,0不同组合进行代值就得到y的值了,比如b=1,c=0时y为1 所以此时对应的真值表的一行应该是 0,1,0,1以此类推:B=0...1年前查看全部

- 用真值表判断公式的类型 p→(p∨q∨r)

天使丽人布艺1年前1

天使丽人布艺1年前1 -

yxm2333 共回答了18个问题

yxm2333 共回答了18个问题 |采纳率94.4%p→(p∨q∨r) 0 0 0 0 假→假 命题为真0 0 0 1 假→真 命题为真0 0 1 0 假→真 命题为真0 0 1 1 假→真 命题为真1 1 0 0 真→真 命题为真1 1 0 1 真→真 命题为真1 1 1 0 真→真 命题为真1 1 1 1 真→真 命题为真有...1年前查看全部

- 如题,给出真值表,求电路的表达式是______?

如题,给出真值表,求电路的表达式是______?

无具体表..有无规范化得步骤或者表达式? 7pk30mp51年前3

7pk30mp51年前3 -

火警电话119 共回答了17个问题

火警电话119 共回答了17个问题 |采纳率88.2%有固定的步骤:(1)找出输出值为1的所有情况,在列表达式时,这些情况是“或”逻辑;(2)针对上面找到的每个所有1 的情况,输入值为1的项,则不作改变,输入值为0的项,则变为非本身.然后项与项之间是与逻辑;例如:输入...1年前查看全部

- 1. 用最少的门电路设计一个满足以下给出真值表的逻辑电路.要求:(1)写出最简的逻辑表达式;(2)画出Y1 、Y2的逻辑

1. 用最少的门电路设计一个满足以下给出真值表的逻辑电路.要求:(1)写出最简的逻辑表达式;(2)画出Y1 、Y2的逻辑电路图.

A B Y1 Y2

0 0 1 0

0 1 0 1

1 0 0 1

1 1 0 0 不妖不媚1年前2

不妖不媚1年前2 -

疯疯疯疯子 共回答了13个问题

疯疯疯疯子 共回答了13个问题 |采纳率92.3%都忘的差不多了 ,应该是这样吧 Y1=(A-B-) + (A-B)- + (AB-)- + (AB)-

Y2==(A-B-)- + (A-B) + (AB-) + (AB)- .化简就可以了,貌似不好看懂呢 ,应该是同或和异或吧,哦 差一点 11 001年前查看全部

- 卡诺图与真值表的区别

muqiurong08141年前1

muqiurong08141年前1 -

rj_love 共回答了22个问题

rj_love 共回答了22个问题 |采纳率90.9%真值表是把每个变量的取值都列出来得到逻辑表达式但可能不是最简式

卡诺图是用来化简逻辑表达式 与或式1年前查看全部

- 真值表如何推出逻辑表达式

夕阳刀刀1年前1

夕阳刀刀1年前1 -

tianyu5211314 共回答了17个问题

tianyu5211314 共回答了17个问题 |采纳率82.4%把真值表中输出等于 1 的表达式相加,再化简.

真值表:

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

Y = A'B + AB'

= A♁B ;异或门.

有时输出为 0 的表达式少,也可以用反函数表达,再求反,本题是一样多:

Y' = A'B' + AB

= A⊙B ;同或门,即异或非门.

Y = A♁B1年前查看全部

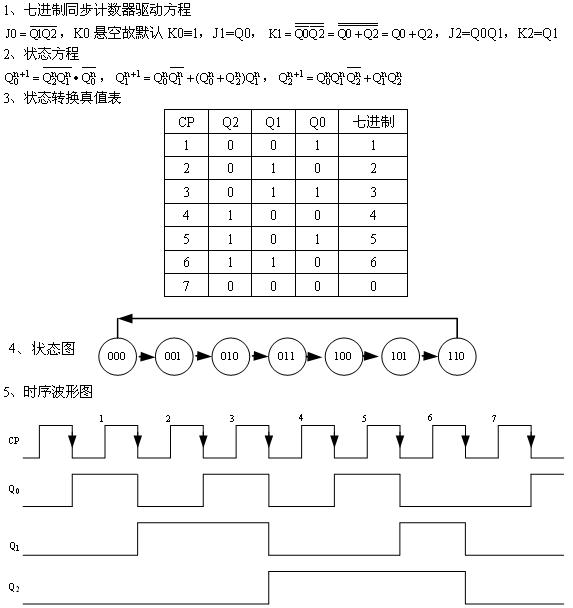

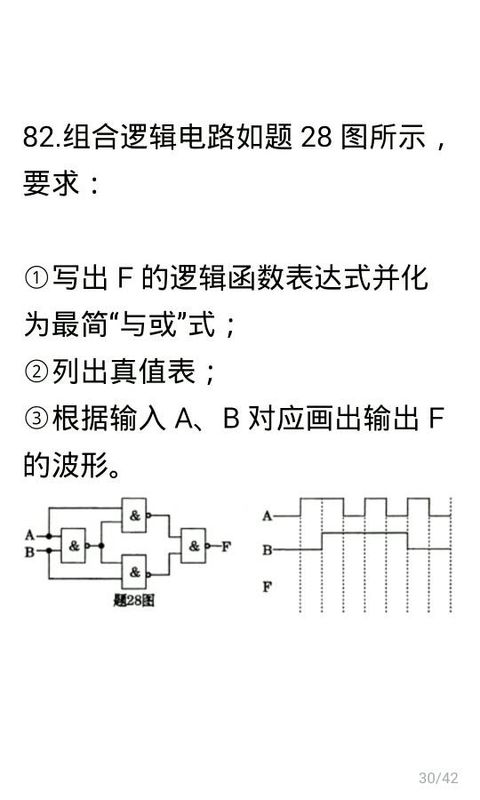

- 组合逻辑电路如题28图所示,要求:①写出F的逻辑函数表达式并化为最简“与或”式; ②列出真值表

组合逻辑电路如题28图所示,要求:①写出F的逻辑函数表达式并化为最简“与或”式; ②列出真值表

组合逻辑电路如题28图所示,要求:

①写出F的逻辑函数表达式并化为最简“与或”式;

②列出真值表;

③根据输入A、B对应画出输出F的波形.

海韵89711年前2

海韵89711年前2 -

youran009 共回答了15个问题

youran009 共回答了15个问题 |采纳率93.3%1年前查看全部

- 如表是某简单逻辑电路的真值表,根据这个真值表可以判断此逻辑电路使用的是______门电路(选填“与”、“或”、“非”),

如表是某简单逻辑电路的真值表,根据这个真值表可以判断此逻辑电路使用的是______门电路(选填“与”、“或”、“非”),表中的“X”的取值为______.

输入 输出 A B Z 0 0 0 0 1 X 1 0 1 1 1 1  sevenP1年前1

sevenP1年前1 -

雨夜的游隼 共回答了20个问题

雨夜的游隼 共回答了20个问题 |采纳率85%解题思路:会根据逻辑电路的真值表推断逻辑关系、逻辑门电路.输入为“1,1”“1,0”输出为“1”,输入“0,0”输出为“0”,知该门电路是或门,所以输入“0,1”,输出为1.

故答案为:或,1.点评:

本题考点: 简单的逻辑电路.

考点点评: 或门的特点是只要有一个条件满足,事件就能发生,与门的特点是条件全部满足,事件才能发生,非门的特点是输入状态和输出状态完全相反.1年前查看全部

- 已知组合逻辑电路如下图所示,写出真值表及输出表达式,分析该电路的功能(可以用来做什么)

找寻幸福De鱼1年前1

找寻幸福De鱼1年前1 -

哀伤的糖果 共回答了22个问题

哀伤的糖果 共回答了22个问题 |采纳率95.5%Y = (A + B + C)' + (A +B')' + B'

= A'B'C' + A'B + B'

= B' (A'C' + 1) + A'B

= B' + A'B

= A' + B'

= (AB)'

二输入端与非门 .1年前查看全部

- 如图是逻辑电路图,真值表中当A为1,B为0时,输出Z的值为( ) A.O B.1 C.O或1 D.任意值

馨怡1年前1

馨怡1年前1 -

_小橥_ 共回答了19个问题

_小橥_ 共回答了19个问题 |采纳率78.9%图示是或门符号,故满足或逻辑关系,当A为1,B为0时,输出Z的值为1

故选B1年前查看全部

大家在问

- 1已知点M(-1,√2,1)关于y轴和xOz平面的对称点分别为M1,M2,求MM2

- 2关于人具有不屈不挠品质的成语,

- 3The meat in that supermarket looks_____and is sold_____

- 4现代汉语中一个词的词性应该如何判断

- 5英语介词的用法电影院在图书馆楼上.这句话应该如何翻译?用介词on吗?感觉很不对啊?

- 6英语选择he is seen ____ in the park every morningA.walk B.walks

- 7After (catch),the thief told the truth

- 8[2/5]加上[3/5]乘[2/3]的积,和是多少?

- 9“我是你人生中一个渺小的过客”帮我翻译成英文

- 10【数学题】已知,如图所示Rt△ABC中,∠C=90°,点O在AB上,以O为圆心,OA长为半径的圆与AC、AB分别交于点

- 11有一根长7.5米的条形钢材,要分别裁成长0.5米、0.6米的甲乙两种毛胚,以便进一步加工成钢轴.要使钢材不浪费应当如何裁

- 12(2013•岳阳模拟)青春期男女,身心显著变化的主要原因是( )

- 13翻译英语“和你单独在一起的时候我不紧张”

- 14读“黄河流域”图,完成下列各题:

- 15五分之八的二分之一比一个数的25%少0.2,求这个数.