D触发器的符号和特性

美联社长2022-10-04 11:39:540条回答

美联社长2022-10-04 11:39:540条回答

已提交,审核后显示!提交回复

共0条回复

相关推荐

- JK触发器和D触发器怎样迅速判断JK触发器的J,K各端的好坏?实验验证怎样迅速判断D触发器各端的好坏?实验验证

琴声刺骨1年前1

琴声刺骨1年前1 -

猪马核 共回答了16个问题

猪马核 共回答了16个问题 |采纳率81.3%触发器是具有记忆功能的二进制存储器件,是各种时序逻辑电路的基本器件之一.其结构有同步、主从、维持阻塞等三种电路.触发器按功能可分为RS触发器,JK触发器,D触发器和T触发器等;按电路的触发方式可分为主—从触发器和边沿触发器(包括上升边沿触发器和下降边沿触发器)两大类.目前我国生产的TTL集成触发器主要有边沿D触发器,边沿JK触发器与主—从JK触发器等.利用这些触发器可以转换成其他功能的触发器,但转换成的触发器其触发方式并不改变.例如由边沿变换来的仍是边沿触发方式的触发器.

由两个与非门交叉耦合而成的基本RS触发器是各种触发器的最基本组成部分,能存储一位二进制信息,但存在R+S=1的约束条件,即R端与S端的输入信号不能同时为0.

一个集成触发器通常有三种输入端,第一种是异步置位、复位输入端,用SD、RD表示.如输入端有一个圈,则表示用低电平驱动,当SD或RD端有驱动信号时,触发器的状态不受时钟脉冲与控制输入端所处状态的影响.第二种是时钟输入端,用CP表示,在SD=RD=1情况下,只有CP脉冲作用时才能使触发器状态更新.如CP输入端没有小圈,表示在CP脉冲上升沿时触发器状态更新,如CP输入端有小圈,则表示在CP脉冲下升沿时触发器状态更新.第三种是控制输入端,用D、J、K等表示.加在控制输入端的信号是触发器状态更新的依据.1年前查看全部

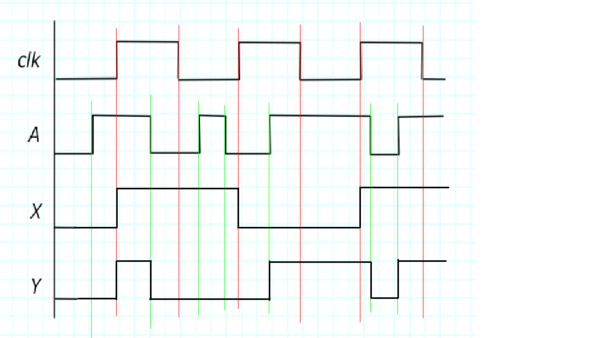

- 关于D触发器和D锁存器的问题在这样的数字电路中当输入信号clk和A为输出信号X和Y分别为什么?

梅森_那是北呀1年前1

梅森_那是北呀1年前1 -

fjl1982727 共回答了22个问题

fjl1982727 共回答了22个问题 |采纳率90.9%1年前查看全部

- 用两个D触发器实现一个异步四进制计数器电路,要求画出逻辑图~

一等良民哦1年前0

一等良民哦1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- D触发器中,在CP=1,D=0的条件下,使触发器置1该怎么做?

D触发器中,在CP=1,D=0的条件下,使触发器置1该怎么做?

这是西科大的实验课后思考题,学的太差 品茗521年前1

品茗521年前1 -

地下hh123 共回答了13个问题

地下hh123 共回答了13个问题 |采纳率84.6%可以使用置1端 使其输出端置11年前查看全部

- 用D触发器能组成计数器吗?

白话001年前1

白话001年前1 -

pengyou5211314 共回答了17个问题

pengyou5211314 共回答了17个问题 |采纳率82.4%可以.对N个D触发器组成的级联结构的最后输出Q或者Q非的高电平(计1)或者低电平(计0)进行计数,即可以实现计数器的功能.例如时钟源的频率是100HZ,则最终输出端就会以100/2的N次方 的频率进行计数.

推广:

分频电路的核心就是计数器电路,一般分频电路里都要用到D触发器进行2分频,也可实现一个脉冲上升沿或者下降沿翻转一次的目的;

用途1:把第一个D触发器的输出Q接第二个触发器的输入端D,这样一个D触发器可实现2分频,2个可实现4分频,N个可实现2的n次方分频.就构成了扭环型计数器,亦称约翰逊计数器.

用途2:利用一个脉冲上升沿或者下降沿翻转一次的特性,把翻转后的输出接回时钟输入端,做控制用,就可以实现小数的分频,这个在脉冲分频里也有广泛的应用.1年前查看全部

- 2个D触发器组成的电路如图所示,设定初态Q2Q1=00,经3个CP脉冲作用后,触发器的状态应Q2Q1是

2个D触发器组成的电路如图所示,设定初态Q2Q1=00,经3个CP脉冲作用后,触发器的状态应Q2Q1是

A 00 B 01 C 10 D 11

我在自学电子技术基础

誰忘了承諾1年前1

誰忘了承諾1年前1 -

huboy 共回答了28个问题

huboy 共回答了28个问题 |采纳率85.7%Q1(n+1)=^Q2n

Q2(n+1)=Q1n;

那三个时钟之后

选C咯.101年前查看全部

- 数字电路设计 D触发器能组成计数器吗?具体的电路图?

mrlin10081年前0

mrlin10081年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 数字逻辑:哪个大大 教下!1.用D触发器做存储元件,设计一个同步时序逻辑电路,实现两位二进制数加法计数计功能2.用4选1

数字逻辑:哪个大大 教下!

1.用D触发器做存储元件,设计一个同步时序逻辑电路,实现两位二进制数加法计数计功能

2.用4选1的选择器74153实现函数F(A,B,C)=∑m(1,2,3,6)的逻辑功能 happyhui1231年前1

happyhui1231年前1 -

榕易 共回答了22个问题

榕易 共回答了22个问题 |采纳率90.9%program lx;

var a,b,i,c,d:integer;

s1,s2,s3:string;

begin

write('input:');

readln(a,b);

i:=1;

s1:='';

s2:='';

s3:='';

c:=a+b;

while a>0 do begin

s1:=chr(a mod 2+ord('0'))+s1;

a:=a div 2;

i:=i+1;

end;

i:=1;

while b>0 do begin

s2:=chr(b mod 2+ord('0'))+s2;

b:=b div 2;

i:=i+1;

end;

i:=0;

while c>0 do begin

s3:=chr(c mod 2+ord('0'))+s3;

c:=c div 2;

i:=i+1;

end;

val(s1[0],a,d);

val(s2[0],b,d);

val(s2[0],c,d);

if a-b >0 then begin

for i:=1 to c-a do begin s1:=' '+s1; s2:=''+s2 end;

for i:=1 to a-c do s2:=' '+s2;

writeln(' ',s1);

writeln('+ ',s2)

end else begin

for i:=1 to c-b do begin s1:=' '+s1; s2:=''+s2 end;

for i:=1 to b-a do s1:=' '+s1;

writeln(' ',s1);

writeln('+ ',s2)

end;

writeln('--------------');

writeln(' ',s3);

readln;

end.1年前查看全部

- 设计一个8位减法计数器电路(7,6…0循环).用D触发器实现

设计一个8位减法计数器电路(7,6…0循环).用D触发器实现

求门电路图.. zhriddle1年前1

zhriddle1年前1 -

冰蓝MM 共回答了24个问题

冰蓝MM 共回答了24个问题 |采纳率87.5%你可以先做熟悉的事,就是用D触发器构成8位的加计数器,然后取反,如此就得到减计数器了;1年前查看全部

- d触发器和与非门怎样才能构成jk触发器呢

TonoDevasky1年前1

TonoDevasky1年前1 -

love_yr_enemies 共回答了13个问题

love_yr_enemies 共回答了13个问题 |采纳率92.3%这个问题很简单的 教你方法嘛 首先写出2个触发器的特性方程.D触发器为:Q^(n+1)=D;JK触发器为:Q^(n+1)=J*(!Q^n)+!K*Q^n.注(!表示"非").联立2个方程可以解得:D=J*!Q^n+!K*Q^n.好了现在就可以画出电路图了是这样的:D触发器的Q非和J相与,这个我们暂时叫A;然后把K取非(经过一个非门)再和D出发的Q相与,我们暂时称为B,最后我们把A和B相或,输出端接在D触发器的D端,这样就从D触发器转变成JK触发器了.遇到类似都一样,先写出特性方程,然后联立求解.就完了呵呵.1年前查看全部

- 用d触发器设计异步十进制计数器要有原理图快点还有分加

biao775201年前2

biao775201年前2 -

青蛙爱宝贝 共回答了15个问题

青蛙爱宝贝 共回答了15个问题 |采纳率100%应该是

利用D触发器构成计数器

数字电路实验设计:D触发器组成的4位异步二进制加法计数器

2009-12-14 19:09

一、选用芯片74LS74,管脚图如下:

说明:74LS74是上升沿触发的双D触发器,D触发器的特性方程为

二、设计方案:

用触发器组成计数器.触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数.如果把n个触发器串起来,就可以表示n位二进制数.对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成.下图是由D触发器组成的4位异步二进制加法计数器.

三、实验台:

四、布线:

1、将芯片(1)的引脚4、10连到一起,

2、将芯片(2)的引脚4、10连到一起,

3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,

4、将芯片(1)的引脚10连到+5V;

5、将芯片(1)的引脚1、13连到一起,

6、将芯片(2)的引脚1、13连到一起,

7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,

8、将芯片(1)的引脚13连到+5V;

9、将芯片(1)的引脚3接到时钟信号CP

10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚11

11、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚3

12、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚11

13、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q3

14、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V.

五、验证:

接通电源on,默认输出 原始状态0000

每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、11111年前查看全部

- 数字逻辑电路问题!急设计一个模4计数器.要求计数代码为典型格林码,用JK触发器实现,写出完整实验过程用D触发器实现T触发

数字逻辑电路问题!急

设计一个模4计数器.要求计数代码为典型格林码,用JK触发器实现,写出完整实验过程

用D触发器实现T触发器的逻辑功能,画出电路图(可以根据需要选用适当的逻辑门)

用与非门设计一个组合逻辑电路.该电路输入为一位十进制的8421码,当其值大于或等于8和小于等于3时输出 F值为1,否则F的值为0. benybingo1年前1

benybingo1年前1 -

zhangjingwen 共回答了14个问题

zhangjingwen 共回答了14个问题 |采纳率92.9%第一题用2个触发器实现,高位Q1,低位Q0

J0=Q1非,K0=Q1,J1=Q0,K1=Q0非

时钟可用同步时序电路设计

第二题为(Q3非*Q2)的非 4至7的特点就是最高位是0,次高位是11年前查看全部

- 求数字电路大神指导小白!请画出电压波形图!这是D触发器,初态为Q=0

huazai0071年前1

huazai0071年前1 -

grane_lu 共回答了17个问题

grane_lu 共回答了17个问题 |采纳率94.1%D=Q=0,不管时钟如何变化,Q一直为零.1年前查看全部

- 1.D触发器的应用电路如图1所示,设输出Q的初值为0,那么在时钟脉冲cp的作用下,输出Q为(B)

1.D触发器的应用电路如图1所示,设输出Q的初值为0,那么在时钟脉冲cp的作用下,输出Q为(B)

A 1;B cp;

C 脉冲信号,频率为时钟脉冲频率的1/2;D 0

2.由JK触发器组成的应用电路如图2所示,该触发器的初始值为0,经分析可知道是一个(B)

A 同步二进制加法计数器;

B同步四进制加法计数器;

C同步三进制计数器;

D同步三进制减法计数器

每天一个柚子1年前2

每天一个柚子1年前2 -

蓝的梦 共回答了20个问题

蓝的梦 共回答了20个问题 |采纳率100%第一题怎么选B啊,应该选D啊,它把Q接到了D端,它的特征方程是Qn+1=D,所以这样接了就是D=Qn了,所以就是Qn+1=Qn,就一直保持初始值0不变了啊,答案就是D,不是B,脉冲信号对输出没影响

第二题,你知道JK触发器的特性表吧?全0置0 、J0K1置0、J1K0置1、全1翻转,OK,现在假设起始Q1、Q2都为0(输出为10),在下个脉冲来Q1翻转,Q2也翻转,所以Q1为1,Q2为1(输出为01),再来个脉冲Q1置1,Q2置0(输出为00),再来脉冲Q1翻转,Q2置0,就回到了初始状态,所以一共就三个状态,是2、1、0、所以减法、至于选哪个、C包含D有木有?减法计数器就不是计数器啦?

哥们,哪搞来的题啊、、晕倒、、、1年前查看全部

- 数字电路题,下列描述不正确的是下列描述不正确的是( )a.D触发器具有两个有效状态,当Q=0时触发器处于0态b.移位寄存

数字电路题,下列描述不正确的是

下列描述不正确的是( )

a.D触发器具有两个有效状态,当Q=0时触发器处于0态

b.移位寄存器除具有数据寄存功能外还可构成计数器

c.主从JK触发器的主触发器具有一次翻转性

d.边沿触发器具有前沿触发和后沿触发两种方式,能有效克服同步触发器的空翻现象 ljmyhh2131年前1

ljmyhh2131年前1 -

8wy683977 共回答了19个问题

8wy683977 共回答了19个问题 |采纳率78.9%我觉得选D “能有效克服同步触发器的空翻现象”应改为“能有效克服电平触发器的空翻现象”1年前查看全部

- 急求D触发器的特征方程怎么写

mmqm0021年前1

mmqm0021年前1 -

527827933 共回答了18个问题

527827933 共回答了18个问题 |采纳率88.9%Q的n加1次方=D1年前查看全部

- D触发器和JK触发器组成的计数器的区别?

whe1081年前1

whe1081年前1 -

zhujunjie 共回答了14个问题

zhujunjie 共回答了14个问题 |采纳率100%JK触发器是将J、K端都接1,实现反相.D触发器是直接将~Q端接到本触发器的D端,直接实现反相.原理相同,接法不同.1年前查看全部

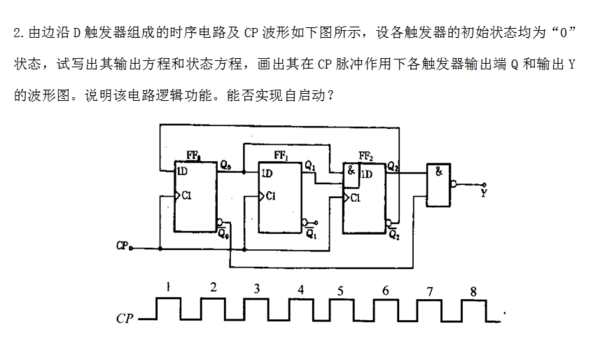

- 由边沿D触发器组成的时序电路及CP波形如下图所示,设各触发器的初始状态均为“0” 状态,试写出其输出方程和状态

由边沿D触发器组成的时序电路及CP波形如下图所示,设各触发器的初始状态均为“0” 状态,试写出其输出方程和状态方程,画出其在CP脉冲作用下各触发器输出端Q和输出Y的波形图。说明该电路逻辑功能。能否实现自启动

八分饱1年前1

八分饱1年前1 -

江南一蒿 共回答了18个问题

江南一蒿 共回答了18个问题 |采纳率100%电路是上升沿同步触发方式,画波形图没诀窍,只要认真、耐心:

Q0(n+1) = Q2'(n)

Q1(n+1) = Q0(n)

Q2(n+1) = Q0(n) * Q1(n)

Y = Q2 * Q0'

画出波形图就能分析电路的功能。1年前查看全部

- 电路上的prn是什么?是什么信号?它是起什么作用的?在D触发器中!

zq18611年前1

zq18611年前1 -

二月三 共回答了18个问题

二月三 共回答了18个问题 |采纳率94.4%PRN - Pseudo Random Noise

伪随机噪声1年前查看全部

- d触发器 通过与非门转为 t触发器

专杀大垃圾61年前1

专杀大垃圾61年前1 -

78190877 共回答了14个问题

78190877 共回答了14个问题 |采纳率92.9%wo you1年前查看全部

- 设计一个8位减法计数器电路(7,6…0循环).用D触发器实现.

珍爱我一生1年前1

珍爱我一生1年前1 -

公紸lily 共回答了30个问题

公紸lily 共回答了30个问题 |采纳率96.7%D触发器可以做二进制的减法计数器,第二级的d触发器cp端接到第一级的q端就可以了 但是d触发器得连接成t’触发器1年前查看全部

- 如何用JK触发器构成D触发器 电路图

huyang10231年前0

huyang10231年前0 -

共回答了个问题

共回答了个问题 |采纳率

大家在问

- 1德语王GM529 电子辞典能查动词变形和名词的词性吗?

- 2一个素数和一个合数的最大公因数要么是1,要么就是那个素数

- 3如图的电路中,R1=40欧姆,R3=20欧姆,电源电压U=12V且保持不变,当S1、S2断开时,电流表的示数为0.1A,

- 4(12分)下表是周期表中的一部分,根据A~I在周期表中的位置,用元素符号或化学式回答下列问题:

- 5从备选词语中选用两个或两个以上的词语,至少运用一种修辞手法,写一段话,谈谈你对“乐观”的理解

- 6英语翻译The Crystal Towers HotelThe WTCA’s EMEA has negotiated s

- 7二元一次方程练习题

- 8"我不会不开心"翻译成英文是什么

- 9匀加速直线运动中的加速度方向一定和位移方向相同

- 10某调查机构对本市小学生课业负担情况进行了调查,设平均每人每天做作业的时间为x分钟.有1000名小学生参加了此项调查,调查

- 11So far, many students in the school ______ a lot of prizes i

- 12我的好朋友帮我 作文600字大神们帮帮忙

- 132011年晚上8点左右烟台发生轻微的地震了么?

- 141.We have not ( ) time to catch the train now.A.adequate B.s

- 15解下列分式方程1600/x=1000/(x-30)