上拉电阻是什么电阻?有什么作用?

lovenhexin2022-10-04 11:39:541条回答

lovenhexin2022-10-04 11:39:541条回答

已提交,审核后显示!提交回复

共1条回复

o0浩瀚0o 共回答了11个问题

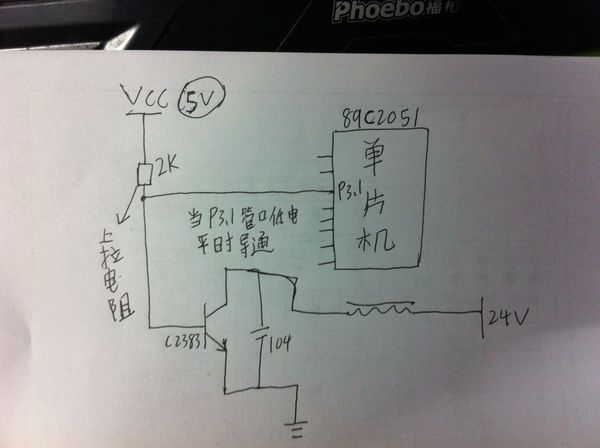

o0浩瀚0o 共回答了11个问题 |采纳率90.9%- 在很多单片机电路中,其I/O管脚检测信号是以高、低电平来判断是否有信号变化的,比如5V为高电平;0V为低电平.那么这些管脚如果不接上拉电阻的话,其电平信号就可能是随机的了,0V~5V之间不一定是什么状态,这样的话单片机就不能正确地判断是不是有信号电平变化了.因此给I/O管脚上接一个上拉电阻使它的检测信号由不确定电平状态拉到5V电平,单片机就能准确地判断是不是有信号变化了.同理,还有下拉电阻,把不确定电平状态拉到0V,使系统更加稳定.

- 1年前

相关推荐

- 上拉电阻的作用有哪些?

aa的烟头11年前3

aa的烟头11年前3 -

Ejosa 共回答了12个问题

Ejosa 共回答了12个问题 |采纳率91.7%上拉电阻功能主要是为集电极开路输出型电路输出电流通道,提高输出高电平的值,加大输出引脚的驱动能力.1年前查看全部

- 为什么上拉电阻可以使引脚高电平?

为什么上拉电阻可以使引脚高电平?

RT,能不能详细地从电路原理上解释

不太明白,能不能详细一点说明?

特别是这里

引脚电压:为上拉电阻与引脚内部阻抗分压 远岭侧峰1年前3

远岭侧峰1年前3 -

玉雨虫 共回答了19个问题

玉雨虫 共回答了19个问题 |采纳率89.5%引脚高阻输出,自身不带偏置.外接上拉后,引脚电压:为上拉电阻与引脚内部阻抗分压,几乎为偏置电压.所以为高电平.

什么叫高阻态?是否理解?

在高阻状态下,输出电阻很大,引脚电压是虚的,不会从外界索取电流,也不能对外界提供电流.就算是很小的负载,也会对其引脚电压产生很大的影响.上拉就变成高电平,下拉就变成低电平.为了给负载提供电流,所以I/O端口需要上拉.1年前查看全部

- 上拉电阻的作用三极管导通的条件是集电极和发射极之间的电压大于基极和发射极之间的电压.如果在基极加一个上拉电阻那不是提高了

上拉电阻的作用

三极管导通的条件是集电极和发射极之间的电压大于基极和发射极之间的电压.如果在基极加一个上拉电阻那不是提高了基极和发射极之间的电压,这样会导致三极管无法导通. ssuperking1年前1

ssuperking1年前1 -

liuke8035 共回答了16个问题

liuke8035 共回答了16个问题 |采纳率87.5%这句话本身就是错误的!

1.三极管导通的一个条件是:基极和发射极之间的电压正向偏置并大于死区电压;

2.集电极与发射极之间的电压也需要正向偏置.

3.三极管饱和导通的时候(Ubes > 0.7V),基极的电位有可能高于集电极的电位.1年前查看全部

- 单片机引脚输入高电平为什么要加上拉电阻?有图,求指导.

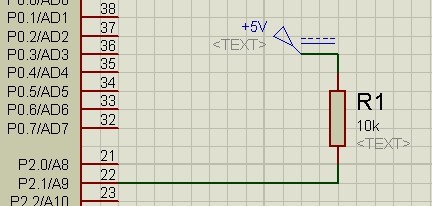

单片机引脚输入高电平为什么要加上拉电阻?有图,求指导.

如图这是我在一个书上看到的例子,意思就是要让这个P2.1口检测一个外加的高电平,我有2点不太懂,1为什么不是5V的电源直接接?要加个上拉电阻.(个人感觉是不是因为直接加了5V电源担心电流过大烧坏单片机?)

2这个上拉电阻书上给出的值是10kΩ,这个值是怎么算出来的? 传说中的雅歌布1年前1

传说中的雅歌布1年前1 -

ysm618 共回答了23个问题

ysm618 共回答了23个问题 |采纳率87%设计单片机控制系统的关健是“抗干扰”.作为输入口使用的时候P2.1直接接上+5V电源是可行的而且“抗干扰”性能最好,但是若作为输出时就会烧坏单片机了所以要加一个限流电阻.

P2.1口内部有上拉电阻为何还要加个外接上拉呢?单片机内部的上拉电阻大约为100K,电流0.05毫安左右,这么小的电流很容易被“干扰”成低电平,接上10K电阻电流可达到0.5毫安“抗干扰”性能大大提高.1年前查看全部

- 上拉电阻接电压时为几伏?高于5V可以吗?

Vera-yang1年前1

Vera-yang1年前1 -

alermy 共回答了5个问题

alermy 共回答了5个问题 |采纳率60%一般上拉电阻,都是接5V电压的,要接比较高的电压的话,建议推动三极管,三极管集电极接上拉电阻.1年前查看全部

- 1、floating signal是什么意思? 2、上拉电阻很重要.如果没有的话,INT/ will float.这里英

1、floating signal是什么意思? 2、上拉电阻很重要.如果没有的话,INT/ will float.这里英语怎么翻译?

魔之魂1年前1

魔之魂1年前1 -

zxm123cs 共回答了14个问题

zxm123cs 共回答了14个问题 |采纳率78.6%floating signal应该是“浮空信号”或“悬空信号”的意思,

也就是说,在一个需要上拉电阻的输出级,如共射输出时,集电极会有一个上拉电阻到电源,然后从集电极输出信号,如果没有上拉电阻,集电极就是悬空的,输出将会有故障(INT),输出极悬空1年前查看全部

- 上拉电阻的接法与单片机和OC门

金色杀虫喷雾1年前3

金色杀虫喷雾1年前3 -

情定中原 共回答了20个问题

情定中原 共回答了20个问题 |采纳率90%一端接电源正极,一端接单片机I/O口.OC门的话也是一样,一端接电源正极,一端接OC门的输出端.1年前查看全部

- 上拉电阻怎么拉高电平?

heishui51年前6

heishui51年前6 -

yuner211314 共回答了17个问题

yuner211314 共回答了17个问题 |采纳率88.2%OC门的输出级三极管截止时,输出电压就接近上拉电阻所连接的高电平电压,因为上拉电阻的阻值比截止状态下三极管C-E间的等效电阻要小得多,而各串连电阻的分压是和电阻阻值成正比的.1年前查看全部

- 上拉电阻和下拉电阻的作用是什么,

TONGTONG511年前4

TONGTONG511年前4 -

kk守门人 共回答了20个问题

kk守门人 共回答了20个问题 |采纳率85%所谓上,就是指高电平;所谓下,是指低电平.上拉,就是通过一个电阻将信号接电源,一般用于时钟信号数据信号等.下拉,就是通过一个电阻将信号接地,一般用于保护信号.

这是根据电路需要设计的,主要目的是为了防止干扰,增加电路的稳定性.

假如没有上拉,时钟和数据信号容易出错,毕竟,CPU的功率有限,带很多BUS线的时候,提供高电平信号有些吃力.而一旦这些信号被负载或者干扰拉下到某个电压下,CPU无法正确地接收信息和发出指令,只能不断地复位重启.

假如没有下拉,保护电路极易受到外界干扰,使CPU误以为被保护对象出问题而采取保护动作,导致误保护.

上拉下拉,要根据电路要求来设置.1年前查看全部

- 上拉电阻 下拉电阻原理图请给一个简单的能说明上拉电阻 下拉电阻作用的原理图,但是没有图的配合,说实话实在有点生涩啊.

weijie8681年前1

weijie8681年前1 -

caomufei 共回答了29个问题

caomufei 共回答了29个问题 |采纳率89.7%需要用到上拉电阻和下拉电阻的情况还蛮多的,画图比较麻烦.

上拉电阻:就是从电源高电平引出的电阻接到输出

1,如果电平用OC(集电极开路,TTL)或OD(漏极开路,COMS)输出,那么不用上拉电阻是不能工作的,这个很容易理解,管子没有电源就不能输出高电平了.

2,如果输出电流比较大,输出的电平就会降低(电路中已经有了一个上拉电阻,但是电阻太大,压降太高),就可以用上拉电阻提供电流分量,把电平“拉高”.(就是并一个电阻在IC内部的上拉电阻上,让它的压降小一点).当然管子按需要该工作在线性范围的上拉电阻不能太小.当然也会用这个方式来实现门电路电平的匹配.

需要注意的是,上拉电阻太大会引起输出电平的延迟.(RC延时)

一般CMOS门电路输出不能给它悬空,都是接上拉电阻设定成高电平.

下拉电阻:和上拉电阻的原理差不多,只是拉到GND去而已.那样电平就会被拉低.下拉电阻一般用于设定低电平或者是阻抗匹配(抗回波干扰).1年前查看全部

- 什么是上拉电阻和下拉电阻,都有什么用?

小小fairy1年前3

小小fairy1年前3 -

羅比 共回答了27个问题

羅比 共回答了27个问题 |采纳率96.3%所谓上,就是指高电平;所谓下,是指低电平.上拉,就是通过一个电阻将信号接电源,一般用于时钟信号数据信号等.下拉,就是通过一个电阻将信号接地,一般用于保护信号.

这是根据电路需要设计的,主要目的是为了防止干扰,增加电路的稳定性.

假如没有上拉,时钟和数据信号容易出错,毕竟,CPU的功率有限,带很多BUS线的时候,提供高电平信号有些吃力.而一旦这些信号被负载或者干扰拉下到某个电压下,CPU无法正确地接收信息和发出指令,只能不断地复位重启.

假如没有下拉,保护电路极易受到外界干扰,使CPU误以为被保护对象出问题而采取保护动作,导致误保护.

上拉下拉,要根据电路要求来设置.1年前查看全部

- 上拉电阻的作用

青色天空大连1年前1

青色天空大连1年前1 -

天地有情_123 共回答了23个问题

天地有情_123 共回答了23个问题 |采纳率82.6%上拉就是将不确定的信号通过一个电阻嵌位在高电平,电阻同时起限流作用,1TTL驱动CMOS时,如果TTL输出最低高电平低于CMOS最低高电平时,提高输出高电平值2 OC门必须加上拉,提高电平值3 加大输出的驱动能力(单片机较常用)...1年前查看全部

- 上拉电阻的功能主要是为集电极开路输出型电路输出电流通道这句话怎样理解?

x当爱已不在x1年前1

x当爱已不在x1年前1 -

my19720402 共回答了24个问题

my19720402 共回答了24个问题 |采纳率79.2%上拉电阻作用: 1,为集电极开路输出型电路“提供”电流通道.不是“输出”电流通道 2,为输入电路提供上偏置,使输入端为高电平1年前查看全部

大家在问

- 1长幼之分 什么意思 谁能用简单文字 详细解释 谢谢你

- 2the old man has two sons,________ is a doctor

- 3商品价格上升,为什么供给增加价格上升,需求量减少,供给量还增加那岂不是卖不出去要亏了么?怎么不是供给减少啊?

- 4谁知道,半圆的周长和面积如何计算

- 5(2014•齐齐哈尔)用一个圆心角为240°半径为6的扇形做一个圆锥的侧面,则这个圆锥底面半径为______.

- 6Lily's too young and her mum doesn't want to leave her ( ) a

- 7The meaning of "a five-sail junk"?

- 884消毒液真的那么有用吗?它是不是跟漂白水一样?

- 9(2010•北京一模)市场上销售的牙膏大部分都是含氟牙膏,含氟牙膏能增强牙齿的坚固性.这里所说的氟是指( )

- 10成语故事勤奋卷 熟能生巧 BY JOYORANGE怎么样

- 11这是最好的时代,这是最坏的时代;这是智慧的年头,这是愚蠢的年头;这是信仰的时代,这是怀疑的时代;这是光明的季节,这是黑暗

- 12找一个与《世说新语》中的《陈太丘与友期》相关或意义一样的小故事

- 13金属单质在反应中只作还原剂

- 14阅读下面文段,完成后面的题。故虽有贤君,不爱无功之臣;虽有慈父,不爱无益之子。是故不胜其任而处其位,非此位之人也;不胜其

- 15解方程:(2t+1)^4-2(2t+1)^2+1=0