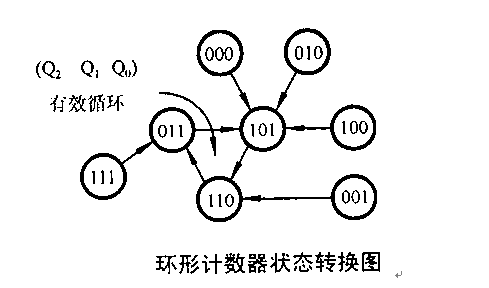

用JK触发器附加必要的门电路,设计一个环形计数器. 已知条件 电路状态转换图如图所示 (1) 设计要求;列

京安2022-10-04 11:39:541条回答

京安2022-10-04 11:39:541条回答

用JK触发器附加必要的门电路,设计一个环形计数器. 已知条件 电路状态转换图如图所示 (1) 设计要求;列

(1)设计要求;列出状态转换表,写出状态转换方程,画出逻辑图和时序图;

(2)仿真测试电路的时序(用发光二极管指示)

已提交,审核后显示!提交回复

共1条回复

advancer365 共回答了22个问题

advancer365 共回答了22个问题 |采纳率86.4%- 我有个以前的数电课设跟你这个有一点点类似,

- 1年前

相关推荐

- 那K端按什么算?也是按1?还有jk触发器的状态方程是J乘以Q的n次方的反还...

那K端按什么算?也是按1?还有jk触发器的状态方程是J乘以Q的n次方的反还...

那K端按什么算?也是按1?还有jk触发器的状态方程是J乘以Q的n次方的反还是J乘以Q反的n次方? 秋天日记1年前2

秋天日记1年前2 -

nita111 共回答了17个问题

nita111 共回答了17个问题 |采纳率88.2%根据电路输入级特点,凡是TTL电路输入端悬空,都等效于输入高电平.所以k端只要悬空,也算作输入1.

JK触发器的状态方程是J乘以Q的n次方的反,再或上K的反乘以Q的n次方1年前查看全部

- 同步JK触发器和主从JK触发器的区别,他们的真值表好像是一样的吧

同步JK触发器和主从JK触发器的区别,他们的真值表好像是一样的吧

还有同步JK触发器中J,K,CP都为1时,我只知道现态由0转变成次态1,但是现态如果是1,用同样的方法分析逻辑电路图却不能得到次态0得到的次态还是1,那岂不是置1啦,而不是翻转, 徐持1年前1

徐持1年前1 -

solo1017 共回答了22个问题

solo1017 共回答了22个问题 |采纳率90.9%逻辑功能都是一样的,主要体现在真值表上.两者区别在于触发时刻的不同,主从触发器存在两步,最后的输出翻转在脉冲下降沿.但是存在主触发器一次翻转特性,同步不存在这个现象.1年前查看全部

- JK触发器和D触发器怎样迅速判断JK触发器的J,K各端的好坏?实验验证怎样迅速判断D触发器各端的好坏?实验验证

琴声刺骨1年前1

琴声刺骨1年前1 -

猪马核 共回答了16个问题

猪马核 共回答了16个问题 |采纳率81.3%触发器是具有记忆功能的二进制存储器件,是各种时序逻辑电路的基本器件之一.其结构有同步、主从、维持阻塞等三种电路.触发器按功能可分为RS触发器,JK触发器,D触发器和T触发器等;按电路的触发方式可分为主—从触发器和边沿触发器(包括上升边沿触发器和下降边沿触发器)两大类.目前我国生产的TTL集成触发器主要有边沿D触发器,边沿JK触发器与主—从JK触发器等.利用这些触发器可以转换成其他功能的触发器,但转换成的触发器其触发方式并不改变.例如由边沿变换来的仍是边沿触发方式的触发器.

由两个与非门交叉耦合而成的基本RS触发器是各种触发器的最基本组成部分,能存储一位二进制信息,但存在R+S=1的约束条件,即R端与S端的输入信号不能同时为0.

一个集成触发器通常有三种输入端,第一种是异步置位、复位输入端,用SD、RD表示.如输入端有一个圈,则表示用低电平驱动,当SD或RD端有驱动信号时,触发器的状态不受时钟脉冲与控制输入端所处状态的影响.第二种是时钟输入端,用CP表示,在SD=RD=1情况下,只有CP脉冲作用时才能使触发器状态更新.如CP输入端没有小圈,表示在CP脉冲上升沿时触发器状态更新,如CP输入端有小圈,则表示在CP脉冲下升沿时触发器状态更新.第三种是控制输入端,用D、J、K等表示.加在控制输入端的信号是触发器状态更新的依据.1年前查看全部

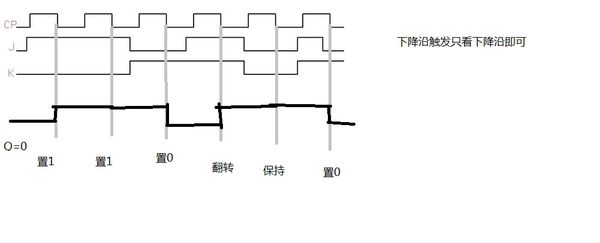

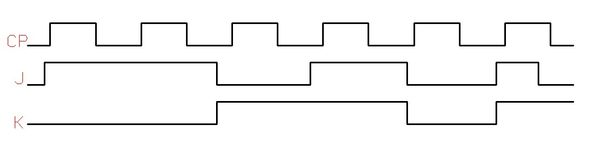

- 已知一下降沿触发器的JK触发器,其输入波形如下,试画出Q的波形图

已知一下降沿触发器的JK触发器,其输入波形如下,试画出Q的波形图

其图如下

nbsnow1年前1

nbsnow1年前1 -

xiaoqiaowanli 共回答了19个问题

xiaoqiaowanli 共回答了19个问题 |采纳率89.5%1年前查看全部

- 多选题哦 JK触发器在CP脉冲作用下,欲使Qn+1=Qn,则输入信号应为____.

多选题哦 JK触发器在CP脉冲作用下,欲使Qn+1=Qn,则输入信号应为____.

a、A.J=K=1

b、B.J=Q,K=Q

c、 C.J=Q,K=Q

d、D.J=Q,K=1 网友netfriend1年前1

网友netfriend1年前1 -

djtc 共回答了23个问题

djtc 共回答了23个问题 |采纳率100%c答案怎么一样呢 Qn+1=JQn'+K'Qn.d肯定对1年前查看全部

- 【急】jk触发器的特性方程?Qn+1=JQn+KQnQ*=JQ'+K'Q区别是什么? 一样吗?

doabefmbs1年前1

doabefmbs1年前1 -

shuiymh 共回答了15个问题

shuiymh 共回答了15个问题 |采纳率93.3%不一样吧,jk触发器的特性方程为:— —

Qn+1=JQn + KQn

也就是说第二个方程是对的,下一个状态等于J乘以上一个状态取非(也就是Qn取非)加上K取非乘以上一个状态Qn,第一个是错的吧1年前查看全部

- 用JK触发器设计一个二进码三进制的同步减法计数器,画出逻辑图!

我同楼1年前0

我同楼1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 试用JK触发器设计一个可逆计数器。

试用JK触发器设计一个可逆计数器。

要求:当X=0时为4进制加法计数器;当X=1时为4进制减法计数器。试画出状态转换图,写出状态方程、输出方程和驱动方程

花的太阳1年前1

花的太阳1年前1 -

ri23901 共回答了22个问题

ri23901 共回答了22个问题 |采纳率81.8%1、十五进制计数器 2、传不了图片(如果你要图片的话,给我你的邮箱号,我发给你) 3、能自动启动1年前查看全部

- 欲使JK触发器实现Qn=Qn+1的功能,则输入端J应接( )K应接( )

欲使JK触发器实现Qn=Qn+1的功能,则输入端J应接( )K应接( )

急!急!

熊玉乐1年前1

熊玉乐1年前1 -

yy老太 共回答了18个问题

yy老太 共回答了18个问题 |采纳率83.3%1和11年前查看全部

- 2. 如果JK触发器的J=0,K=1,则当时钟脉冲出现时,Qn+1为 ( )

2. 如果JK触发器的J=0,K=1,则当时钟脉冲出现时,Qn+1为 ( )

A.1 B.0 C.Q D.-Q

ake76801年前1

ake76801年前1 -

huamingyang1218 共回答了25个问题

huamingyang1218 共回答了25个问题 |采纳率88%J = K = 1 时,Qn+1 = Qn‘,即触发器翻转。

J = 1,K = 0 时,Qn+1 = 1 ;

J = 0,K = 1 时,Qn+1 = 0 ;

J = K = 0 时,Qn+1 = Qn ;

J = K = 1 时,Qn+1 = Qn' ;1年前查看全部

- JK触发器5个作用端(J,K,CP,Sd反,Rd反)的作用?请分别说明,

kelly_cq911年前1

kelly_cq911年前1 -

HC的HD 共回答了14个问题

HC的HD 共回答了14个问题 |采纳率92.9%j,k是输入端,cp是时钟信号输入,sd反是异步置位,rd反是复位端,亲,若满意,请采纳1年前查看全部

- 主从型JK触发器,当CP=1时,若JK=11,则Qn+1=()注:n+1是在Q右下角的一个整体

主从型JK触发器,当CP=1时,若JK=11,则Qn+1=()注:n+1是在Q右下角的一个整体

若CP由1变为0时,则Qn+1=()注:n+1是在Q右下角的一个整体 kunlunshanzi1年前2

kunlunshanzi1年前2 -

兔兔990 共回答了24个问题

兔兔990 共回答了24个问题 |采纳率87.5%发生翻转.Qn=0,那么Qn+1=1.Qn=1,那么Qn+1=01年前查看全部

- 求解一道电工学试题!逻辑电路如图所示,试分析A等于Q和A不等于Q两种情况下的JK触发器具有何种功能.

xulintj1年前0

xulintj1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- d触发器和与非门怎样才能构成jk触发器呢

TonoDevasky1年前1

TonoDevasky1年前1 -

love_yr_enemies 共回答了13个问题

love_yr_enemies 共回答了13个问题 |采纳率92.3%这个问题很简单的 教你方法嘛 首先写出2个触发器的特性方程.D触发器为:Q^(n+1)=D;JK触发器为:Q^(n+1)=J*(!Q^n)+!K*Q^n.注(!表示"非").联立2个方程可以解得:D=J*!Q^n+!K*Q^n.好了现在就可以画出电路图了是这样的:D触发器的Q非和J相与,这个我们暂时叫A;然后把K取非(经过一个非门)再和D出发的Q相与,我们暂时称为B,最后我们把A和B相或,输出端接在D触发器的D端,这样就从D触发器转变成JK触发器了.遇到类似都一样,先写出特性方程,然后联立求解.就完了呵呵.1年前查看全部

- 用JK触发器和附加门电路设计一个七进制加法计数器,要解题的详细步骤,拜谢了

langzchanchu_4181年前0

langzchanchu_4181年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 数字逻辑电路问题!急设计一个模4计数器.要求计数代码为典型格林码,用JK触发器实现,写出完整实验过程用D触发器实现T触发

数字逻辑电路问题!急

设计一个模4计数器.要求计数代码为典型格林码,用JK触发器实现,写出完整实验过程

用D触发器实现T触发器的逻辑功能,画出电路图(可以根据需要选用适当的逻辑门)

用与非门设计一个组合逻辑电路.该电路输入为一位十进制的8421码,当其值大于或等于8和小于等于3时输出 F值为1,否则F的值为0. benybingo1年前1

benybingo1年前1 -

zhangjingwen 共回答了14个问题

zhangjingwen 共回答了14个问题 |采纳率92.9%第一题用2个触发器实现,高位Q1,低位Q0

J0=Q1非,K0=Q1,J1=Q0,K1=Q0非

时钟可用同步时序电路设计

第二题为(Q3非*Q2)的非 4至7的特点就是最高位是0,次高位是11年前查看全部

- JK触发器中j和k分别是什么意思呢?

千雨千浔1年前1

千雨千浔1年前1 -

shalizlm 共回答了13个问题

shalizlm 共回答了13个问题 |采纳率92.3%在扑克牌中K代表国王,J是侍从.黑桃K是公元前10世纪的以色列国王索洛蒙的父亲戴维,他善用竖琴演奏,并在圣经上写了许多赞美诗,所以黑桃K画面上经常有竖琴图样.红桃K是查尔斯一世弗兰克国王,他叫沙勒曼,是四张国王牌中唯一不留胡须的国王.方块K是罗马帝国的国王、名将和政治家凯萨,是四张国王牌中唯一一张侧面像.梅花K是最早征服世界的马其顿帝国国王亚力山大,他的衣服上总是佩戴着配有十字架的珠宝.黑桃J和方块J分别为查尔斯一世的侍从霍克拉和洛兰.红桃J为查尔斯七世的侍从拉海亚.梅花J是阿瑟王故事中的著名骑士兰斯洛特.主从jk触发器由此而来.1年前查看全部

- 主从JK触发器,边沿JK触发器有什么区别

jun19869141年前1

jun19869141年前1 -

甜蜜的小花 共回答了16个问题

甜蜜的小花 共回答了16个问题 |采纳率81.3%边沿触发器最大的特点就是仅在电平变化的边沿那一瞬间外界翻转激励才有效.相对jk主从,优点在于稳定性好,激励电平只需要保证在边沿一小段时间稳定即可,受外界干扰的窗口也小.1年前查看全部

- 这样消除JK触发器里的一次变化现象

用我生命忘记爱1年前2

用我生命忘记爱1年前2 -

严厉打击非典 共回答了18个问题

严厉打击非典 共回答了18个问题 |采纳率94.4%当J=0,K=0时,两个与门阻.无论Q、Q非何态S,R为低电平,不会改变QQ状态.J=1,K=0时,上门阻.无置位可能.若Q=1,下门通.CLK正沿到达时,触发器复位;若Q=0,下门阻.即使K=1,也不产生任何动作,Q仍为0 J=1,K=0时 R不能为高电平.下门阻.无置位可能.若Q=0 上门通.CLK正沿时,Q=1; 若Q=1 下门阻.上下门均阻.Q不变为1; J=1,K=1时 可能置位或复位.若原状态 Q=0,CLK来时会使Q=1,反之 Q=1,CLK来时会使Q=0,计数器就是利用JK触发器翻转原理作成的

这样说来,复位即可1年前查看全部

- 数字电路实验 JK触发器和门电路设计计数器

数字电路实验 JK触发器和门电路设计计数器

RT,是同步计数器的设计,需要设计一个12进制的计数器,即从01——>12再返回01,如此循环,希望有人能帮助提供一下思路分析,并给出电路图参考, 家乡美丽1年前2

家乡美丽1年前2 -

kuankuanyu5 共回答了19个问题

kuankuanyu5 共回答了19个问题 |采纳率84.2%JK触发器和门电路组成的同步计数器电路“和“计数回到我阔别多年的母校-实验小学,我去的时候简直不敢1年前查看全部

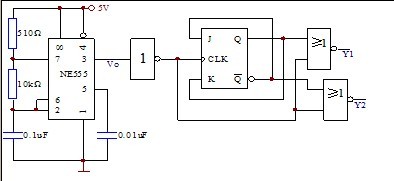

- 由NE555定时器、JK触发器及门电路构成的两相时钟发生器如图7所示

由NE555定时器、JK触发器及门电路构成的两相时钟发生器如图7所示

(1)计算NE555定时器构成的多谐振荡器输出VO的周期T及脉宽TWH,(2)对应画出VO及Y1、Y2的波形.

xy86491年前1

xy86491年前1 -

lifei7758 共回答了14个问题

lifei7758 共回答了14个问题 |采纳率78.6%振荡周期 T=0.7*(R1+R2)*C,脉宽 TWH==(R1+R2)/(R1+2R2) 后面的自己仿真吧.1年前查看全部

- 急,三个jk触发器组成计数器最多有效状态是几个

急,三个jk触发器组成计数器最多有效状态是几个

rt wangyepippo1年前1

wangyepippo1年前1 -

k22963 共回答了22个问题

k22963 共回答了22个问题 |采纳率90.9%我懂的,挺有意思的,要相信我哦有``1年前查看全部

- 边沿JK触发器的特性方程是?

香芋酥酥1年前1

香芋酥酥1年前1 -

weity 共回答了13个问题

weity 共回答了13个问题 |采纳率84.6%Q(n+1)=JnQn(非)+Kn(非)Qn .1年前查看全部

- 请问主从JK触发器和边沿JK触发器VHDL语言有什么不同?

nilan_1999_19991年前1

nilan_1999_19991年前1 -

huxinting 共回答了21个问题

huxinting 共回答了21个问题 |采纳率85.7%由于主从触发器只有在CP=1期间输入的J、K状态始终未变的条件下,用CP的下降沿才能保证锁存住正确的触发器次态,否则需要根据CP=1期间输入的J、K变化的具体情况才能确定CP下降沿到达时触发器的次态.所以,采用行为描述的方式,很难描述主从JK触发器,只能采用结构描述或者RTL描述的方式,来描述主从JK触发器.

而边沿触发器不存在上述问题,因此可以很方便地用行为描述方式来描述下降沿JK触发器:

IF CP'EVENT AND CP='0' THEN

CASE J&K IS

WHEN "10" => Q1年前查看全部

- D触发器和JK触发器组成的计数器的区别?

whe1081年前1

whe1081年前1 -

zhujunjie 共回答了14个问题

zhujunjie 共回答了14个问题 |采纳率100%JK触发器是将J、K端都接1,实现反相.D触发器是直接将~Q端接到本触发器的D端,直接实现反相.原理相同,接法不同.1年前查看全部

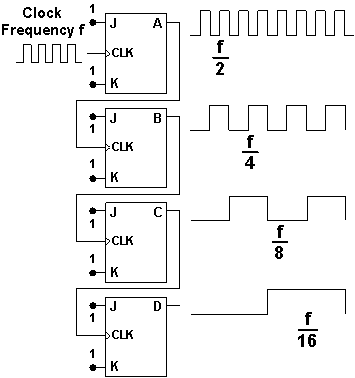

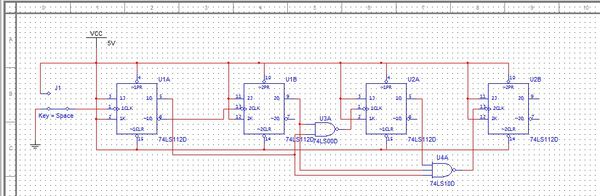

- JK触发器构成四位二进制异步计数器

JK触发器构成四位二进制异步计数器

如图,这个图原理上有没有什么问题?为什么结果不对? 六月课堂1年前1

六月课堂1年前1 -

waterinfo 共回答了17个问题

waterinfo 共回答了17个问题 |采纳率88.2%1年前查看全部

- JK触发器与RS触发器的构成与区别?

仲夏然梦1年前0

仲夏然梦1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- Jk触发器 英文是什么

ajingaialing1年前1

ajingaialing1年前1 -

蓝伊伊 共回答了16个问题

蓝伊伊 共回答了16个问题 |采纳率87.5%Jk触发器:JK (Jump-Key)flip-flop

相应的有RS触发器:RS (Reset-Set) flip-flop

T触发器:T (Toggle) flip-flop

使用触发器作flip-flop的译名不但意思不完整且极容易与trigger相混淆,产生翻译混乱,建议翻作双态触发器.

In digital circuits,a flip-flop is a term referring to an electronic circuit (a bistable multivibrator) that has two stable states and thereby is capable of serving as one bit of memory.Today,the term flip-flop has come to mostly denote non-transparent (clocked or edge-triggered) devices,while the simpler transparent ones are often referred to as latches; however,as this distinction is quite new,the two words are sometimes used interchangeably1年前查看全部

- JK触发器的J、K分别是哪个英文单词的字头?

送四刀1年前1

送四刀1年前1 -

prince宝宝 共回答了20个问题

prince宝宝 共回答了20个问题 |采纳率90%Jack 、Kilby 美国人 Jack St.Clair Kilby (杰克.基尔比),集成电路发明者,J-K触发器是以杰克.基尔比命名的.1年前查看全部

- 如何用JK触发器构成D触发器 电路图

huyang10231年前0

huyang10231年前0 -

共回答了个问题

共回答了个问题 |采纳率

大家在问

- 1什么时候14+10会等于1

- 2关于"保护噪音污染"的英语作文含意思30

- 3It means you will have to come visit me though!

- 4爱迪生和富兰克林具有什么的精神

- 5一个三位数,他的个位数比百位数小5十位上的数比个位上的数大3,这个数在900至1000这个数是多少?

- 6阅读下列诗句,结合地理知识,探究诗中蕴涵的物候现象。

- 7下列属于第二次工业革命成就的有①爱迪生发明电灯②德国人卡尔·本茨试制汽车成功③莱特兄弟研制飞机成功④发电机和电动机的发明

- 8相册用英语怎么说?

- 9连词成句.1,north,school,our,is,park,the,of2,tries,again,uses,he,

- 10将家蚕发育的各个阶段按正确顺序排列

- 11质量为2kg的物体放在水平面上,在F=12N的水平拉力下,产生的加速度为3m/s2,经过时间t速度为vt,若从此开始,水

- 12直线方程的问题1 已知直线L过点(1,1),且被两条平行直线3X-4Y-13=0与3X-4Y+7+0截得的线段长为四倍根

- 13下列现象与空气的什么成份有关:饼干在空气中放置久了会变软——、澄清的石灰水敞口放置会变浑浊——

- 14Do you have any apples?(改为同义句)

- 15英语翻译看好,是2011八月新GRE作文题目,不要老的,老的我手上有,我会仔细看的.argument的翻译我悬赏150分