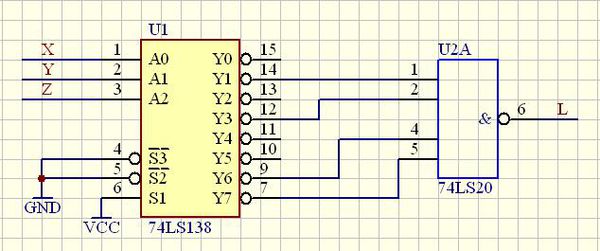

38线译码器与138与非门实现与或非的逻辑函数y=AB+BC

hanfanyan2022-10-04 11:39:541条回答

hanfanyan2022-10-04 11:39:541条回答

已提交,审核后显示!提交回复

共1条回复

生日是uu庆节 共回答了18个问题

生日是uu庆节 共回答了18个问题 |采纳率83.3%- 将逻辑函数y=AB+BC展开为最小项表达式,然后把与这些最小项相对应的138输出端分别接到与非门的输入端即可

- 1年前

相关推荐

- 电子信息工程的题目填空15三态输出门的三个输出状态分别是( )、( )和( ).7.n个输入端的二进制译码器共有( )个

电子信息工程的题目填空1

5三态输出门的三个输出状态分别是( )、( )和( ).

7.n个输入端的二进制译码器共有( )个最小项输出.

8.根据用途分,存储器分为两大类.一类是( )另一类是( ).

9.a/d转换器是将( )转换为( ).

16.逻辑电路按其输出信号对输入信号响应的不同,可以分为( )两大类.

17.存在空翻现象的触发器是( )触发器.

18.组成一个模为60的计数器,至少需要( )个触发器.

19.若两个逻辑函数具有相同的( ),则认为该两个逻辑函数相等.

20.三态门主要用于( )传送电路信号.

21.用低电平代表逻辑1,高电平代表逻辑0,这种逻辑***称为( )逻辑.

22.对于共阳型led数码管,应选用输出( )电平的显示译码器.

23.jk触发器与rs触发器的显著区别是( ).

24.触发器的触发方式是由电路的( )决定的.

25.时序逻辑电路按其触发器有否统一时钟控制可分为( )时序电路

和( )时序电路.

26.n个触发器最大可构成( )进制计数器.

27.串联负反馈在信号源内阻( )时反馈效果显著;并联负反馈在信号源内阻( )

时反馈效果显著.

28.根据反馈信号在输出端的取样方式不同,可分为( )反馈 和( )反馈 ,根据反馈信号和输入信号在输入端的比较方式不同,可分为( )反馈和( )反馈 .

29.集成运放用作电压比较器时,应工作于( )环状态或引入( )反馈. 菲常真人1年前1

菲常真人1年前1 -

xle51 共回答了19个问题

xle51 共回答了19个问题 |采纳率84.2%5、高阻、高电平、低电平

7、2的n次方

8、RAM、ROM

9、模拟量,数字量

16、组合逻辑电路,时序逻辑电路

17、RS触发器

18、6

19、真值表

20、多路

21、负

22、低

23、可靠性高,没有空翻.

24、结构

25、同步,异步

26、2的n次方

27、小,大

28、电压,电流,串联,并联

29、开,正1年前查看全部

- 用译码器74LS138和适当的逻辑门实现下列函数:F=AB+BC(要画图)

叔叔有练过1年前0

叔叔有练过1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 下列逻辑电路中为时序逻辑电路的是 .A、译码器 B、加法器 C、寄存器 D、数据选择器

brucej1年前1

brucej1年前1 -

不喜欢喝水 共回答了14个问题

不喜欢喝水 共回答了14个问题 |采纳率78.6%C1年前查看全部

- 数字电子题目试用3线-8线译码器54LS138和门电路产生如下多输出逻辑函数(画出接线图)Y1=ACY2=ˉAˉBC+A

数字电子题目

试用3线-8线译码器54LS138和门电路产生如下多输出逻辑函数(画出接线图)

Y1=AC

Y2=ˉAˉBC+AˉBˉC+BC

Y3=ˉBˉC+ABˉC

说明:ˉA表示A非 92098901年前1

92098901年前1 -

呵呵喝 共回答了21个问题

呵呵喝 共回答了21个问题 |采纳率85.7%1年前查看全部

- 下面哪个不是组合逻辑电路:译码器 编码器 全加器 寄存器

风中掠影1年前1

风中掠影1年前1 -

情倾小楼 共回答了11个问题

情倾小楼 共回答了11个问题 |采纳率90.9%寄存器,它是时序逻辑.1年前查看全部

- 如图所示电路,是由74HC138译码器实现组合逻辑函数,根据电路写出表达式并化简

铁血墨龙1年前0

铁血墨龙1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 用三片3线-8线74ls138组成5线-24线译码器

雪山松鼠1年前1

雪山松鼠1年前1 -

liuhongty 共回答了17个问题

liuhongty 共回答了17个问题 |采纳率82.4%用三片3线-8线74ls138组成5线-24线译码器,74LS138有三条选择输入线既 A,B,C.片脚为脚1,脚2,脚3.把三片74LS138的A,B,C,分别并联在一起,既每条线上连有3个A,3个B,3个C.这样,占去了5条线的3条.还剩两条线,用于控制三片74LS138的使能输入.使能控制有3个脚,叫为 G1,G2A,G2B.74LS138集成块,

6脚=G1,4脚=G2A,5脚=G2B

真值表公式 G2=G2A+G2B 当G1=H, G2=L 时 集成块被选通.

设:剩的两条用于使能控制的线为 K1,K2,三片74LS138集成块分别叫U1,U2,U3.

使U1的G1接5V,U1的G2A连K1,U1的G2B连K2,U2的G1连K1,U2的G2A和G2B连一起连K2,U3的G1连K2,U3的G2A和G2B连一起连K1.

这样,当K1,K2两条线分别等于 0 0,0 1,和 1,0 时,就能分别选通U1,U2,U3三个集成块中的其中一片.1年前查看全部

- 大神在那里?学霸在那里!一、填空1、求解暂态过程的简便方法是___________.2、译码器工作时执行的是编码器的__

大神在那里?学霸在那里!

一、填空

1、求解暂态过程的简便方法是___________.

2、译码器工作时执行的是编码器的___________过程.

3、复合门电路包括有___________、___________、___________和___________.

二、简答题

集成触发器有哪两个基本特征?

电工方面的高手来帮忙解答一下 can_yan1年前1

can_yan1年前1 -

John_lee 共回答了17个问题

John_lee 共回答了17个问题 |采纳率94.1%一、填空

1、求解暂态过程的简便方法是__三要素法__.

2、译码器工作时执行的是编码器的__反编译__过程.

3、复合门电路包括有__与门___、___或门__、___异或门___和___非门____.

二、简答题

集成触发器有哪两个基本特征?

有两个稳定的逻辑状态,在输入信号的作用下,触发器可以从一个稳定状态转换到另一个稳定状态.输入信号变化前的触发器状态称为现态,输入信号变化后的触发器状态称为次态.1年前查看全部

- 试用一片4线—16线译码器74154和与非门设计能将8421BCD码转换为格雷码的代码转换器.(主要不知道这个图怎么画,

试用一片4线—16线译码器74154和与非门设计能将8421BCD码转换为格雷码的代码转换器.(主要不知道这个图怎么画,求这个图)

abczhy123451年前1

abczhy123451年前1 -

lnch8113 共回答了30个问题

lnch8113 共回答了30个问题 |采纳率93.3%1年前查看全部

- 分别用3-8译码器74ls138和四选一数据选择器实现Y=AB+BC+AC,画接线图

danshsh1年前0

danshsh1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 用3线—8线译码器(74LS138芯片).四输入与非门实现"三个开关控制一个灯的电路",要求改变任一开关的状态都能控制改

用3线—8线译码器(74LS138芯片).四输入与非门实现"三个开关控制一个灯的电路",要求改变任一开关的状态都能控制改变灯的状态(亮或灭).

柠檬耳环1年前0

柠檬耳环1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 七段译码器为什么不显示数字?

hyjdj1年前2

hyjdj1年前2 -

田下有力 共回答了27个问题

田下有力 共回答了27个问题 |采纳率81.5%你说的是七段数码管吧?七段译码器是个译码器,自然不会显示数字了.

七段译码管的话还得看你的译码管是共阳极的还是共阴极的,你的电路上这样看是共阴极的,如果要显示哪几段,就要将对应段的电位设置为低电平,当然,你接地就是低电平了,如果是七段数码管,你少了DP脚,就是小数点显示位.如果是共阴极的,那么你这电路本身就是错误的.1年前查看全部

- 请试用一片74HC138译码器来实现函数L(A,B,C,D)=ABC+ACD.74HC138译码器不是只有3个输入端?为

请试用一片74HC138译码器来实现函数L(A,B,C,D)=ABC+ACD.74HC138译码器不是只有3个输入端?为什么可以控制A,B,C,D四个输入变量?

佛前一炷香1年前1

佛前一炷香1年前1 -

rbz1980 共回答了20个问题

rbz1980 共回答了20个问题 |采纳率95%提示:的确是3个控制端,但第4个变量一般使用1和0代替,你可以参考书上相关例子.哪里不清欢迎追问,1年前查看全部

- 已知74LS138译码器的输入三个使能端(E1=1,E2A = E2B=0)时,地址码A2A1A0=011,则输出 Y7

已知74LS138译码器的输入三个使能端(E1=1,E2A = E2B=0)时,地址码A2A1A0=011,则输出 Y7 Y0是( ) .

CGHA1年前1

CGHA1年前1 -

00008098 共回答了19个问题

00008098 共回答了19个问题 |采纳率100%000010001年前查看全部

- 试用3线——8线译码器74LS138和门电路实现下面多输出逻辑函数 Y1=AC Y2=ABC+ABC+BC Y3=ABC

试用3线——8线译码器74LS138和门电路实现下面多输出逻辑函数 Y1=AC Y2=ABC+ABC+BC Y3=ABC+BC

Alex5821年前1

Alex5821年前1 -

bmwboyliu 共回答了16个问题

bmwboyliu 共回答了16个问题 |采纳率100%很简单啊电子技术基础 P1981年前查看全部

- 38译码器 左下角的100是神马,如果不是100那是什么东西? 左边abc端124,那可以421么,以及为何

38译码器

左下角的100是神马,如果不是100那是什么东西? 左边abc端124,那可以421么,以及为何是abc ,就左边这堆符号我看不大明白,右边和中间的英文我就不画了,主要是abc,124,左下角的与符号,EN英文和100,以及100为啥1不取非而00都要取非,

方印1年前1

方印1年前1 -

残念 共回答了19个问题

残念 共回答了19个问题 |采纳率89.5%左下角的100,是这块芯片的功能引脚,100,表示左下角的3的端口都是高电平输入,只有在这个前提下这块芯片才能开始工作.上边的124,表示cba这三个口的权重,说白了就是因为芯片已经由硬件规定好了,a的权重是4,b的权重是2,c的权重是1.他们是不能换的.en是使能端,顾名思义就是说只有en使能了,芯片才能正常工作.1不取非而00都要取非,那是因为00的端口接了反相器,输入为零时,芯片里面才接到的是高电平.1年前查看全部

- 用数字电路的基础器件(比如74LS161计数器和76LS138译码器)可以设计什么实验电路?

用数字电路的基础器件(比如74LS161计数器和76LS138译码器)可以设计什么实验电路?

以前做实验的时候有把161和138连起来用过,设计红绿灯太简单了,有稍微难一点儿的吗? yfg31年前1

yfg31年前1 -

MPMan2k 共回答了15个问题

MPMan2k 共回答了15个问题 |采纳率100%你可以设计一个倒计时的电路呀,比如说,一上电就显示100,然后,开始倒计时,到0就停下来.这就会让你用到好多以前学过的东西了.1年前查看全部

- 用74LS138译码器构成6-64线译码电路,至少需要多少块74LS138译码器?答案是9块.我知道了,但是为什么?

full19841年前1

full19841年前1 -

dxh860613 共回答了9个问题

dxh860613 共回答了9个问题 |采纳率66.7%用8个138,分别构成8个3-8译码器,故共有64个输出端;

用1个138,构成1个3-8译码器,控制上述8个译码器的使能端.

所以,用9个,即可.1年前查看全部

- 用3线-8线译码器和门电路设计组合逻辑电路,使Y=BC+AB

freeflyingdzf1年前1

freeflyingdzf1年前1 -

davis31400 共回答了21个问题

davis31400 共回答了21个问题 |采纳率90.5%A0,A1,A2分别对应为A,B,C信号.假设A2是高位信号.

由译码器原理可以知道,当AB=1时,即CBA输入为110或者111.这时Y6或Y7有效.

同理,当BC=1时,即CBA输入为011或111.这时Y3或Y7有效.

所以只要将Y3,Y6,Y7接在一个三端的或门上就行了1年前查看全部

- 关于数字逻辑电路“74ls138是3/8译码器,即对3个输入信号进行译码.得到8个输出状态.G1,G2A,G2B,为数据

关于数字逻辑电路

“74ls138是3/8译码器,即对3个输入信号进行译码.得到8个输出状态.

G1,G2A,G2B,为数据允许输出端,G2A,G2B低电平有效.G1高电平有效.A,B,C为译码信号输出端,Y0~Y7为译码输出端,低电平有效.

需要使能和控制的,只是看它悬空是高电平还是低电平 ”最后一句话中的悬空是指什么?悬空是什么悬空? J清N茶J1年前1

J清N茶J1年前1 -

黄莎莎 共回答了22个问题

黄莎莎 共回答了22个问题 |采纳率100%悬空就是该管脚既不接高电平也不接低电平,什么也不接.这时电路上电会处于一种不定状态,就会出现可能是高电平,可能是低电平.也就是你所说的“悬空是高电平还是低电平”.使用电路中最好不要悬空.1年前查看全部

- 1、典型的组合逻辑电路有:A、译码器 B、计数器 C、加法器 D、编码器

1、典型的组合逻辑电路有:A、译码器 B、计数器 C、加法器 D、编码器

1、典型的组合逻辑电路有:

A、译码器

B、计数器

C、加法器

D、编码器

2、二进制译码具有以下特点:

A、输入n位二进制代码,输出有n个相互独立的有效信号.

B、输入n位二进制代码,输出有2的n次方个相互独立的有效信号.

C、每输入一组二进制代码,只有与其对应的输出端信号无效,其他输出端信号有效.

D、每输入一组二进制代码,只有与其对应的输出端信号有效,其他输出端信号无效.

E、每一个输出函数都是n位地址变量的一个最小项.

3、七段共阴极数码管:

A、要用输出为高电平有效的七段显示译码器来驱动.

B、要用输出为低电平有效的七段显示译码器来驱动.

C、若要显示数据8,abcdefg=1111111.

D、若要显示数据8,abcdefg=1000001.

4、数据选择器是:

A、能够从多路输入数据中选出多路作为输出的组合电路.

B、数据选择器的输出具有最简与或表达式的形式.

C、能够从多路输入数据中选出一路作为输出的组合电路.

D、数据选择器的输出具有标准与或表达式的形式,提供了地址变量的全部最小项.

5、74LS151集成芯片:

A、是一个8选1数据选择器.

B、属于组合逻辑电路.

C、属于时序逻辑电路.

D、是一个3/8译码器. Maya-er1年前1

Maya-er1年前1 -

jitingyu 共回答了18个问题

jitingyu 共回答了18个问题 |采纳率88.9%1. A、C、D

2. D、E

3. A、C

4. C、D

5. A、B1年前查看全部

- 数电题 下列描述不正确的是a.译码器、数据选择器、EPROM均可用于实现组合逻辑函数.b.寄存器、存储器均可用于存储数据

数电题 下列描述不正确的是

a.译码器、数据选择器、EPROM均可用于实现组合逻辑函数.

b.寄存器、存储器均可用于存储数据.

c.将移位寄存器首尾相连可构成环形计数器

d.上面描述至少有一个不正确 wxfaiai1年前0

wxfaiai1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 试用74LS138译码器实现如下逻辑函数:F(A,B,C)=∑M(0,1,3,4,6) 求

试用74LS138译码器实现如下逻辑函数:F(A,B,C)=∑M(0,1,3,4,6) 求

试用74LS138译码器实现如下逻辑函数:F(A,B,C)=∑M(0,1,3,4,6) 求解

veryqin1年前1

veryqin1年前1 -

金麟天罡 共回答了17个问题

金麟天罡 共回答了17个问题 |采纳率88.2%74ls138的输出为Y0',Y1'......Y7'

Y0'对应为输入(A,B,C)=(0,0,0),Y1'=(1,0,0),Y3'=(1,1,0).......Y6'...

将5个Y'输出加非门後加或门,也可以用与非门得出逻辑函数F。1年前查看全部

- 下列电路中,不属于组合逻辑电路的是()A译码器 B全加器 C寄存器 D编码器

yuhang8601091年前1

yuhang8601091年前1 -

eonb6an 共回答了26个问题

eonb6an 共回答了26个问题 |采纳率80.8%当然是寄存器.1年前查看全部

- 关于数字电路3线—8线译码器的问题

关于数字电路3线—8线译码器的问题

试用3线—8线译码器74LS138及必要的门实现一个判别电路.输入为三位二进制代码,当输入代码能被5整除时输出为1,否则为0,要求列出判别电路的真值表,并画出逻辑图. 飘渺疯子1年前1

飘渺疯子1年前1 -

悠悠在天边 共回答了21个问题

悠悠在天边 共回答了21个问题 |采纳率90.5%这个电路应该很简单,不用画真值表,要不然反而走了弯路.

三位二进制输入代码译码后为0-8,其中能被5整除的只有0和5.当没有代码输入时,74LS138的8个输出端都呈现高电平.你可以把74LS138输出端的0、5脚接到一个2输入与非门,74LS138输出的其它引脚悬空,与非门输出端的电平就可以达到你的要求了.

希望这能帮到你!1年前查看全部

- 将2线4线的译码器扩展成3线8线的译码器

将2线4线的译码器扩展成3线8线的译码器

回答时请详细点,最好配图,使用的芯片为74LS139 哈七八搭1年前0

哈七八搭1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 试用74LS138译码器实现如下逻辑函数:F(A,B,C)=∑M(0,2,4,6)

866201621年前1

866201621年前1 -

蓝CS-SX 共回答了19个问题

蓝CS-SX 共回答了19个问题 |采纳率89.5%如图所示..,当输入为A'B'C'=0时,只有Y0输出端为0,其余均为1,那么Z1输出为1,Z2输出为0,所以Z3输出为1;当输入为A'B'C=1时,只有Y1输出端为0,其余均为1,那么,Z1输出为0,Z2输出也为0,所以Z3输出为0....1年前查看全部

- 用一个74LS138译码器实现逻辑函数 F=A`B`C`+A`BC`+AB`C`+ABC

chwl201年前1

chwl201年前1 -

M男宠 共回答了19个问题

M男宠 共回答了19个问题 |采纳率94.7%A`B`C`对应000,为0输出端口;第二项对应010,为2端口;以此类推,第三项为端口6,第四项为端口7,将这四个输出端口接与门即可1年前查看全部

- 用3线—8线译码器74LS138实现逻辑函数∑(1,3,4,5,6)

用3线—8线译码器74LS138实现逻辑函数∑(1,3,4,5,6)

如题.我想了很久不会呀,我是这方面菜鸟 紫色的故事1年前0

紫色的故事1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 74LS151是( )。A. 8线—3线优先编码器 B. 3线—8线译码器 C. 八选一数据选择器 D. 双四选一数据选

74LS151是( )。

A. 8线—3线优先编码器 B. 3线—8线译码器

C. 八选一数据选择器 D. 双四选一数据选择器

ckfc1年前1

ckfc1年前1 -

wjsr 共回答了16个问题

wjsr 共回答了16个问题 |采纳率100%C. 八选一数据选择器1年前查看全部

- 十里加急!译码电路—彩灯控制:在89C51单片机应用板上,扩展一片74LS138译码器,外扩六片74LS373锁存器,每

十里加急!

译码电路—彩灯控制:在89C51单片机应用板上,扩展一片74LS138译码器,外扩六片74LS373锁存器,每个锁存器位线驱动一个发光二极管,要求:按自己的爱好,设计一种图案,编制程序,使图形每秒变化一种. 百色小小不小1年前1

百色小小不小1年前1 -

坎儿 共回答了17个问题

坎儿 共回答了17个问题 |采纳率88.2%说穿了,就是相当于做一个流水灯的程序,只是把流水灯的灯的位置变一下,摆个什么图形,当然可能一个时刻不止一个灯亮,也就是要加好驱动.1年前查看全部

- 用3线—8线译码器74LS138和门电路产生以下逻辑函数的逻辑图(设计一个表决器)

用3线—8线译码器74LS138和门电路产生以下逻辑函数的逻辑图(设计一个表决器)

F1=BC+ABC+ABC(第一个ABC中B上面有一根上划线,第二个ABC中C上面有一根上划线)

xrh123lcn1年前1

xrh123lcn1年前1 -

violet101624 共回答了15个问题

violet101624 共回答了15个问题 |采纳率93.3%F1=BC+AB'C+ABC' = BC(A+A')+AB'C+ABC' = ABC+A'BC+AB'C+ABC'设74ls138的A0输入为A,A1为B和A2为C,从74ls138直值表对应输出, ABC=Y'7=0,A'BC=Y'6=0,AB'C=Y'5=0,ABC'=Y'3=0,所以 F1'=Y'7+Y'6+Y'5+Y'3 F1=...1年前查看全部

- 关于数字电子技术存在很久的疑问上面是译码器和编码器的真值表.红圈里面的就是我不能理解的了,第一幅图:红圈里右到左是从0~

关于数字电子技术存在很久的疑问

上面是译码器和编码器的真值表.红圈里面的就是我不能理解的了,第一幅图:红圈里右到左是从0~7,但第二幅图为什么右到左是从7~0的呢?

如果要我画 真值表那我怎么画呢? 不能理解.

能看懂我说的是什么问题吗?不能我可以再说再说再说 libo8011211年前1

libo8011211年前1 -

aa茶叶 共回答了19个问题

aa茶叶 共回答了19个问题 |采纳率94.7%译码器就是把一个BCD码(四位二进制的数合起来表示一个十进制的数(你图中只有三位能表示1-8))转成一个七段码(就是能接数码管,用来显示数字的,数码管有七段,有的还有一个小数点.)

所以输入是三个变量(随便取什么名字都行),输出有七个

编码器和译码器原理相反,它是把1-7单个的数(意义上的十进制,实际上的二进制)用BCD码表示出来

所以输入有7个,输出只有三个.1年前查看全部

- 44、下列电路中,属于时序电路的是( ).A.编码器 B.译码器 C.数据选择器 D.计数器

兰黑1年前1

兰黑1年前1 -

不清楚no 共回答了21个问题

不清楚no 共回答了21个问题 |采纳率90.5%D1年前查看全部

- 用多少个3线—8线译码器74LS138才能扩展成一个6线—64线译码器?

心碎的糖果1年前1

心碎的糖果1年前1 -

heyanqing_001 共回答了15个问题

heyanqing_001 共回答了15个问题 |采纳率93.3%用一片进行高三位译码,8个输出分别用来分别控制8片译码器进行低三位译码.再将这8片的输出(共64个输出)作为(总)译码的输出.

所以是9片.嘎嘎1年前查看全部

- 用3/8译码器74LS138和门电路构成全加器,写出逻辑表达式,画出电路图,

peipei00251年前1

peipei00251年前1 -

hsp777 共回答了20个问题

hsp777 共回答了20个问题 |采纳率90%首先得弄清楚全加器的原理,你这里说的应该是设计1位的全加器.

全加器有3个输入端:a,b,ci;有2个输出端:s,co.

与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7).

这里可以把3-8译码器的3个数据输入端当做全加器的3个输入端,即3-8译码器的输入A、B、C分别对应全加器的输入a,b,ci;将3-8译码器的3个使能端都置为有效电平,保持正常工作;这里关键的就是处理3-8译码的8个输出端与全加器的2个输出的关系.

现在写出全加器和3-8译码器的综合真值表:

(A/a,B/b,C/ci为全加器和译码器的输入,OUT为译码器的输出(0-7),s为加法器的和,co为加法器的进位输出)PS:假定译码器的输出为高电平有效.

A/a B/b C/ci OUT s co

0 0 0 0 0 0

0 0 1 1 1 0

0 1 0 2 1 0

0 1 1 3 0 1

1 0 0 4 1 0

1 0 1 5 0 1

1 1 0 6 0 1

1 1 1 7 1 1

根据上面的真值表,可以设计出电路图:

将3-8译码器的输出OUT(1、2、4、7)作为一个4输入的或门的输入,或门的输出作为加法器的和;将3-8译码器的输出OUT(3、5、6、7)作为一个4输入的或门的输入,或门的输出作为加法器的进位输出.即完成了加法器的设计.

回过头来分析:

当加法器的输入分别为:a=1,b=0,ci=1时,对应3-8译码器的输入为A=1,B=0,C=1,这是译码器对应的输出为OUT(5)=1,其余的为0,根据上面设计的连接关系,s=0,co=1,满足全加器的功能,举其他的例子也一样,所以,设计全加器的设计正确.1年前查看全部

- 用译码器74138配合逻辑门设计电路实现逻辑函数L(X,Y,Z)=XY+X/Z,画出逻辑电路.

用译码器74138配合逻辑门设计电路实现逻辑函数L(X,Y,Z)=XY+X/Z,画出逻辑电路.

后面那个是X非乘以Z 动人的15票1年前1

动人的15票1年前1 -

爪哇ff的公主 共回答了24个问题

爪哇ff的公主 共回答了24个问题 |采纳率87.5%1年前查看全部

- 2个3线-8线译码器组成4线 16线译码器后的两个第8脚和第16脚怎么接?

k39611年前1

k39611年前1 -

wangosuwm 共回答了15个问题

wangosuwm 共回答了15个问题 |采纳率86.7%A0接A0,A1接A1,A2接A2,第一个STA接高电平,第二个STA接第一个的STC组成了A3 ,第二个STC和STB一起接到第一个的STB组成ST非

因为等级太低不能截图 希望你能看懂1年前查看全部

- 求教如图译码器与非门的组合电路的逻辑功能

求教如图译码器与非门的组合电路的逻辑功能

上面的图是电路 下面的是我的真值表,题目问该电路的逻辑功能是:

A数据选择器 B全加器 C数据比较器 d译码器

答案说的是B,

从我的真值表来看,如果把A作为输入的高位,C作为低位(按照输入那里的A0A1A2排布,C应该是高位,A是低位的貌似啊),再把F2作为输出高位,F1作为输出的低位,那么可以说这是一个全加器.只是我对输入那里的高低位的问题表示纠结,就是按照输入那里的A0A1A2排布,C应该是高位,A是低位的貌似啊.

因为应用的时候,往往习惯于把C作为高位,那么我就想不到这是一个全加器啊.

open32461年前1

open32461年前1 -

jsyey1 共回答了21个问题

jsyey1 共回答了21个问题 |采纳率100%A1年前查看全部

- 3线-8线译码器与七段显示译码器有什么不同?

浮云7771年前1

浮云7771年前1 -

evaent 共回答了8个问题

evaent 共回答了8个问题 |采纳率87.5%3线-8线译码是译码器主要是把输入的二进制码翻译成输出信号,七段显示译码器主要是将输入二进制码翻译成数字显示一般是译码器配合七段显示数码管使用1年前查看全部

- 关于时序逻辑电路__.下列电路中,不属于时序逻辑电路的是_______.A.计数器B.触发器 C.寄存器 D.译码器

sket261年前1

sket261年前1 -

紫夜_lovegoogol 共回答了13个问题

紫夜_lovegoogol 共回答了13个问题 |采纳率76.9%D1年前查看全部

- 数字逻辑分析题求解1、分析下图由3线-8线译码器74LS138构成的电路.(1)写出输出Si和Ci的逻辑函数表达式;(2

数字逻辑分析题求解

1、分析下图由3线-8线译码器74LS138构成的电路.

(1)写出输出Si和Ci的逻辑函数表达式;

(2)画出真值表;

(3)说明该电路的逻辑功能.

图在下面补充里,请会做的大大帮个忙啊,感激不尽.

james85501年前1

james85501年前1 -

cm1234 共回答了19个问题

cm1234 共回答了19个问题 |采纳率89.5%1年前查看全部

- 数字逻辑作业:2片38译码器实现8421码到2421码的转换,

彩aa1年前0

彩aa1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 已知显示译码器(七段数码管)的真值表,共阴极和共阳极的显示译码器输出逻辑表达式如何求?

已知显示译码器(七段数码管)的真值表,共阴极和共阳极的显示译码器输出逻辑表达式如何求?

就是已知共阴的真值表,输出abcdefg,想求abcdefg的逻辑表达式,一般来说逻辑表达式都是把1的相加不就完了吗,但是答案写的是0的相加,我想问为什么 gg打kk1年前1

gg打kk1年前1 -

紫烟love 共回答了16个问题

紫烟love 共回答了16个问题 |采纳率75%真值表是根据共阳来算的,共阴时就取反1下

真值表是根据共阴来算的,共阳时就取反1下1年前查看全部

- 用3线-8线译码器74HC138和门电路设计一个全加器

用3线-8线译码器74HC138和门电路设计一个全加器

组合逻辑电路设计 答得完整且正确另加分 真的爱你31年前0

真的爱你31年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 编码器属于组合逻辑门电路,译码器则由触发器构成.这句话对吗

xiangqx1年前1

xiangqx1年前1 -

coneko 共回答了23个问题

coneko 共回答了23个问题 |采纳率87%不对!

编码器和译码器都属于组合逻辑电路.1年前查看全部

- 用74LS138译码器实现如下逻辑函数:F(A,B,C)=∑M(1,3,5)

真爱不悔1年前0

真爱不悔1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 16路抢答器电路设计图,数字电子技术基础(利用 编码器译码器构成)在线等

hummel_liu1年前0

hummel_liu1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 关于电工电子基础实验的相关问题(单级放大电路,组合逻辑电路,译码器,比例求和运算电路,常用电子仪器

关于电工电子基础实验的相关问题(单级放大电路,组合逻辑电路,译码器,比例求和运算电路,常用电子仪器

1.单级放大电路中

(1)为什么所有仪器“共地”?

(2)测量放大器性能指标Au,ri,ro时,为什么不用万用表测量?

(3)分别增大或减少电阻Rbi,Rc,Rl,Re,及电源电压Vcc,对放大器的静态工作点及性能指标有何影响?为什么?

(4)不用示波器观察输出波形,仅用毫伏表测量放大电路的输出电压uo,是否有意义?

2,比例求和运算电路

(1)运放工作时,为什么要调零?

(2)运放的调零能否在开环(无外部负反馈)的状态下进行?为什么?

(3)调试中是要先进行相位补偿还是先调零?为什么?

3,组合逻辑电路的设计与测试

如果门电路的输出无法吸合继电器,请问电路该做如何改进?

4,译码器及其运用

(1)可否用+5V的直流电压直接接到LED数码管的各段输入端检查该管的好坏?为什么?

(2)共阴极和共阳极LED数码管显示器有什么区别?

越快越好,能回答多少回答多少,

5,常用电子仪器的使用

用示波器和低频毫伏表同时测量正弦电压,为什么两者直接读数不一致,这些数据之间应是什么关系? huangsaijie1年前1

huangsaijie1年前1 -

wuqiongangela 共回答了23个问题

wuqiongangela 共回答了23个问题 |采纳率82.6%我来回答一下吧.说实话,本人对模拟并不是很熟悉,现在也还在熟悉工.我的工作主要是单片机编程.挑一些能回答的回答吧.

单级放大电路

1.首先要明确电压的概念.电压只是一个电势差!既然是差,就不是针对一个而言,而是两个,就像运放的差分输入.两个输入端都接信号时,输入为同相-反相.比如你拿一节5V电池,它的电压是1.5V对吧.我们这时说的1.5V是相对地而言的.也就是大地是参考点.但是如果你拿1.5V做参考点呢?那么电池的电压就是0V了.如果两个仪器不共地,那么发送端的信号到了接收端就没有办法被正确接收,因为它们没有统一的参考点.你发送端将5V定义为逻辑1,等接收端接收到以后会按照自己的参考点来判断这个电平.由于不共地,那么很可能会误判,认为他是2V,3V等.

2.放大器的性能指标Au很大,理想运放的Au趋近于无穷大.即,输入一个非常微小的信号,比如几uV,放大器也能把它“无限”放大,以至接近电源电压.我的理解是,在此情况下,你的万用表根本就达不到测量输入的微小信号的精度.Ri和Ro是输入和输出阻抗,Ri是相对于前级电路而言的,表征的是它从信号源索取电流的大小,Ro是相对于后级负载而言的,表征的是驱动负载的能力.这两个参数是计算出来的.

3.对于运放,我觉得不必像三极管那样考虑他的静态工作点.运放是把管子封装在一个黑盒子里,你知道怎么用就行了.电阻的增大和减小你只需要看和放大有关的电阻即可.进行计算就行了.学习,真的没有必要按照书本上来,国内的教材很多都是垃圾,误人子弟.

4.这个是否有意义,要看你的信号是什么类型的.如果是正弦波,那你用万用表测量的只是有效值.

比例求和电路

1.运放为什么要调零.运放的输入级为差分对管形式,但是由于工艺的问题,两个管子肯定不会完全对称,世界上就没有完全一样的东西.所以实际运放的特性必定不是理想的.即当输入为0的时候输出不为0.因此在使用前我们要调零.

要说明的一点是,这在早期的运放中较为常见,现在的芯片一般都有自动调零.具体问题具体分析好了.

2.3.不确定.但是我觉得调零应该是在开环的状态下进行.理想运放就是输入为0时输出为0.当你调零的时候可以认为输入端没有信号,那你反馈回来以后影响谁?影响输入那你此时的输入就不是0了,还如何调零呢.相位补偿这回事不存在.

任何放大器,既然叫放大,那就是增大了信号的幅度.不会影响相位和频率.

译码器

不可以直接加5V,因为数码管就是一个二极管,其正向电阻较小,有一个最大电流限制,一般10几个mA左右.超过的话就会烧掉.要串联电阻才可以.

2一个7段数码管里面有7个二极管,它们都是独立的.所谓共阴就是他们共用一个地,这个地就是COM端.当分别给各个段施加高电平时,对应的段会点亮.所以叫共阴

所谓共阳,就是他们共用一个电源端,这个电源端也是COM端,当分别对各个段施加低电平时,对应的段会被点亮.

5,毫伏表我没用过.不过他们之间的关系应该是根号2倍的关系,即峰值与有效值的关系.1年前查看全部

大家在问

- 1mong的比较级和最高级

- 2一个带分数的分数部分的分子是3,把它化为假分数后分子是38,这样的带分数有()个,是()

- 31 4 9 16 25的数列通式是?

- 4甲乙两个城市相距720千米,一辆汽车从甲城开往乙城用了12小时,回来时每小时多行12

- 5五一节,小艳陪父母外出旅游,买了一个古铜色的工艺品,检验工艺品是否是铜做成的,小艳选用托盘天平、量筒、烧杯和水等,进行了

- 6PH=12的NAOH和PH=4的HCL等体积混合,求混合后溶液PH

- 7船在静水中的速度为xkm/h,水流速度是ykm/h,则船顺流而下的速度为多少?在逆流而上的速度为多少?

- 8推荐一首诗.(要说出它表达的情感.和理由.)

- 9关于看气温和降水图写出气候类型的题目

- 10若|a-1|+(b+2)2=0,(a+b)2002+a2001=______.

- 11英语翻译七点半左右,我会到!应该怎么翻译就是一条消息!我将在19:30左右到,可以么?或者我将在晚上七点半左右到可以么?

- 12张宇和李云进行射击比赛,每打中一发得20分,脱靶一发倒扣12分,两人各打了10发,共得208分.

- 13求英语翻译 虽然希望很渺茫 我仍要坚持 尝试了可能会失败 不试试永远不会成功

- 14对下列环境描写,判断分析不当的一项是( ) 1.正是严冬天气,彤云密布,朔风渐起,却早纷纷扬扬卷下一天

- 15古代诗歌阅读(16分)鹧鸪天苏轼 林断山明竹隐墙,乱蝉衰草小池塘。翻空白鸟时时见,照水红蕖细细香。村舍外,古城旁,杖藜